## COM92C451

T-75.37.05

# **Combination UART/Printer Interface**

### **FEATURES**

- ☐ Fully IBM PC®, PC XT®, PC AT® Compatible

- ☐ Easily Interfaces to Most Popular Microprocessors

- ☐ Replaces Both the 16C450 and Parallel Port to Reduce Cost and Space

- ☐ Compatible with Industry Standards 16C450 and 82C50A

- ☐ Fully Programmable UART Characteristics:

- 5-, 6-, 7-, or 8-Bit Characters

- 1, 1.5, or 2 Stop Bit Generation

- Even, Odd, or No Parity Bit Generation and Detection

- Baud Rate Generator (DC to 625 KBaud)

- ☐ Internal Programmable **Baud Rate Generator Allows** Division of Any Input Clock by 1 to 65,535 to Generate 16x Clock of up to 10 MHz

- ☐ Provides Full Individual Modem Control Functions

- ☐ Independent and Prioritized Transmit, Receive, Line Status, and Modem Interrupts

- ☐ False Start Bit Detection

- ☐ Complete Status Reporting Capabilities

- ☐ Line Break Generation and Detection

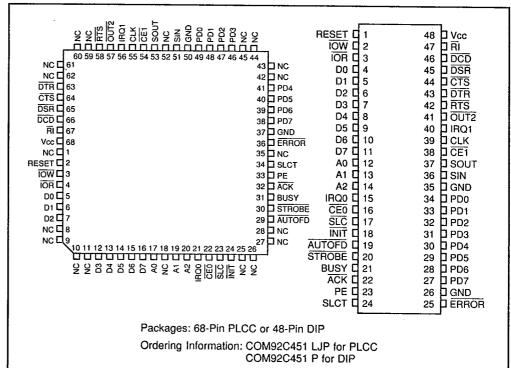

#### PIN CONFIGURATION

- ☐ Internal Diagnostics Capabilities Include:

- Loopback Controls for Communications Link Fault Isolation and

- Break, Parity Overrun, Framing Error Simulation

- ☐ Full Double Buffering to Eliminate Need for Precise Synchronization Between CPU and Serial Data

- ☐ Independent Receiver Clock Input

- ☐ High Impedance TTL Drive Capabilities for Bidirectional Data Bus and Control Bus

- ☐ Fully Compatible with Centronics Parallel Port

- ☐ Provides Latched Data and Control Signals to Printer

- ☐ Provides Printer Status Port

- ☐ Low Power CMOS, +5V Supply

## **GENERAL DESCRIPTION**

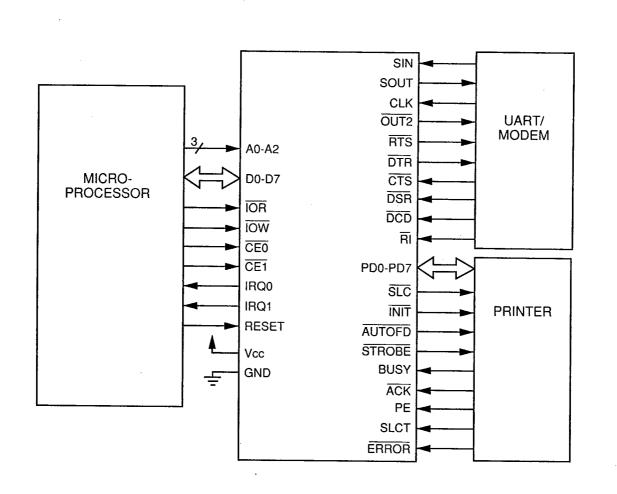

The COM92C451 is a CMOS device which is fully compatible with the IBM PC/AT and may reside on the motherboard to replace both a serial data input/output interface and a parallel port. The serial port is a UART with special modem control signals. The system software configures the UART via the 8-bit bidirectional data bus.

The UART performs serial-to-parallel conversions on data characters received from peripheral devices or modems. and parallel-to-serial conversions on data characters from the microprocessor. The UART includes a programmable baud rate generator capable of dividing the input clock by 1 to 65,535, generating a 16x clock of up to 10 MHz, giving a maximum baud rate of 625 KBaud. Individual, prioritized interrupts can be programmed to the requirements of the user, providing utmost flexibility.

The Parallel Port contains a bidirectional parallel data port which may store information from the UART en route to the printer. The parallel port also contains a control register and a status register, allowing the microprocessor to fully communicate with the printer.

The registers of the COM92C451 are addressable via the A0-A2 bus and the microprocessor may communicate with the registers at any time by reading or writing the information on the D0-D7 lines.

## TABLE OF CONTENTS

| FEATURES                            | .1  |

|-------------------------------------|-----|

| PIN CONFIGURATION                   | . 1 |

| GENERAL DESCRIPTION                 |     |

| DESCRIPTION OF PIN FUNCTIONS        | .3  |

| SYSTEM DESCRIPTION                  | .5  |

| MICROPROCESSOR INTERFACE            | .5  |

| PRINTER INTERFACE                   | .5  |

| UART/MODEM INTERFACE                |     |

| FUNCTIONAL DESCRIPTION              | .6  |

| PRINTER INTERFACE ADAPTER           |     |

| Data Register                       | .7  |

| Control Register                    | .7  |

| Status Register                     | .7  |

| ASYNCHRONOUS COMMUNICATIONS ELEMENT |     |

| Programmable Baud Rate Generator    | .7  |

| Line Control Register               | .8  |

| Line Status Register                | .9  |

| Modem Control Register              | 10  |

| Modem Status Register               |     |

| Interrupt Identification Register   | 11  |

| Interrupt Enable Register           | 11  |

| Scratchpad Register                 | 11  |

| OPERATIONAL DESCRIPTION             | 12  |

| MAXIMUM GUARANTEED RATINGS          | 12  |

| DC CHARACTERISTICS                  | 12  |

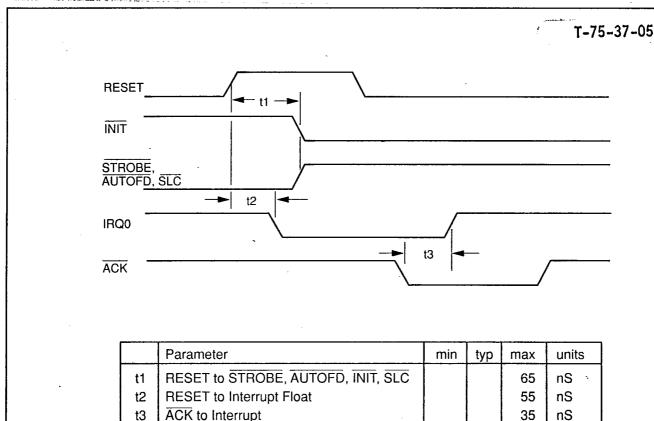

| TIMING DIAGRAMS                     | 13  |

## **DESCRIPTION OF PIN FUNCTIONS**

T-75-37-05

| PLCC            | DIP                 | FINTONOTI               |          |                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

|-----------------|---------------------|-------------------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| PIN NO.         | PIN NO.             | NAME                    | SYMBOL   | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |

| PROCES          | PROCESSOR INTERFACE |                         |          |                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

| 17, 19-20       | 12-14               | Address<br>0-2          | A0-A2    | Input. These signals are used to decode the registers of the Asynchronous Communications Element (ACE) or printer Interface Adapter (PIA).                                                                                                                                                                                                                 |  |  |  |  |  |  |

| 5-7, 12-16      | 4-11                | Data 0-7                | D0-D7    | Input/Output. These signals are used to transfer data, status, and control words between the COM92C451 and the microprocessor. These signals are in the high impedance state when not active.                                                                                                                                                              |  |  |  |  |  |  |

| 4               | 3                   | I/O Read                | IOR<br>、 | Input. This active low signal is used by the microprocessor to read data from the COM92C451. A low level on this pin outputs data onto the D0-D7 pins.                                                                                                                                                                                                     |  |  |  |  |  |  |

| 3               | 2                   | I/O Write               | IOW      | Input. This active low signal is used by the microprocessor to write data to the COM92C451. The data is latched onto the D0-D7 pins on the rising edge of this signal. A low level on this pin and on CE0 and CE1 simultaneously puts the COM92C451 into an ACE Baud Rate Test Mode.                                                                       |  |  |  |  |  |  |

| 22              | 16                  | <u>Chip</u><br>Enable 0 | CE0      | Input. This active low signal is used to enable the PIA. Whenever access to the Printer Interface is required, this signal must be held stable at a logic "0". A low level on this pin and on IOW and CE1 simultaneously will put the COM92C451 into the ACE Baud Rate Test Mode. A low level on CE0 and CE1 without IOW held low is an illegal condition. |  |  |  |  |  |  |

| 54              | 38                  | <u>Chip</u><br>Enable 1 | CE1      | Input. This active low signal is used to enable the ACE. Whenever access to the ACE is required, this signal must be held stable at a logic "0". A low level on this pin and on IOW and CE0 simultaneously will put the COM92C451 into the ACE Baud Rate Test Mode. A low level on CE0 and CE1 without IOW held low is an illegal condition.               |  |  |  |  |  |  |

| 21              | 15                  | Interrupt<br>Request 0  | IRQ0     | Output. This active high signal is used by the PIA to interrupt the processor. This signal is enabled by setting bit 4 of the Printer Interface Control Register to a logic "1", and is otherwise in the high impedance state.                                                                                                                             |  |  |  |  |  |  |

| 56              | 40                  | Interrupt<br>Request 1  | IRQ1     | Output. This active high signal is used by the ACE to interrupt the processor. This signal is enabled by setting the appropriate bits in the Interrupt Enable Register to a logic "1" (see the Internal Registers section of this document).                                                                                                               |  |  |  |  |  |  |

| 2               | 1                   | Reset                   | RESET    | Input. This active high signal resets the COM92C451 to its initial state. A hard reset clears the Data Register and the Control Register of the PIA and clears all registers of the ACE except for the Receiver Buffer, the Transmitter Holding Register and the Divisor Latches.                                                                          |  |  |  |  |  |  |

| PARAL           | LEL INTER           | RFACE                   |          |                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

| 49-46,<br>41-38 | 34-37               | Printer<br>Data 0-7     | PD0-PD7  | Input/Output. These signals carry the data stored in the Printer Interface Data Register to and from the printer via non-inverting buffers.                                                                                                                                                                                                                |  |  |  |  |  |  |

| 23              | 17                  | Printer<br>Select       | SLC      | Output. This active low, open-drain signal is used to select the printer. This signal is the complement of bit 3 of the Printer Control Register and is in the high impedance state when not active.                                                                                                                                                       |  |  |  |  |  |  |

| 24              | 18                  | Initiate                | INIT     | Output. This active low, open-drain signal is used to clear the printer buffer. This signal is bit 2 of the Printer Control Register and is in the high impedance state when not active.                                                                                                                                                                   |  |  |  |  |  |  |

| 29              | 19                  | Auto Feed               |          | automatically. This signal is the complement of bit 1 of the Printer Control Register and is in the high impedance state when not active.                                                                                                                                                                                                                  |  |  |  |  |  |  |

| 30              | 20                  | Strobe                  | STROBE   | Output. This active low, open-drain signal is used to strobe the printer data into the printer. This signal is the complement of bit 0 of the Printer Control Register and is in the high impedance state when not active.                                                                                                                                 |  |  |  |  |  |  |

| DIP<br>N NO.<br>INTERF<br>21 | NAME                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | SYMBOL                                                                                                                                                                                                                                                                             | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                              |

|------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                              | - A O C / O O N I T I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                    | DESURIF HUN                                                                                                                                                                                                                                                                                                                                                                              |

| 21 I                         | ACE (CONT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                          |

| -1                           | Busy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | BUSY                                                                                                                                                                                                                                                                               | Input. This active high signal is used to tell the COM92C451 that the printer is not ready to receive new data. This signal is the complement of bit 7 of the Printer Status Register.                                                                                                                                                                                                   |

| 22                           | Acknow-<br>ledge                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ACK                                                                                                                                                                                                                                                                                | Input. This active low signal is used to tell the COM92C451 that the printer has received the data and is ready to accept new data.  This signal is bit 6 of the Printer Status Register.                                                                                                                                                                                                |

| 23                           | Paper End                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | PE.                                                                                                                                                                                                                                                                                | Input. This active high signal is used to tell the COM92C451 that the printer is out of paper. This signal is bit 5 of the Printer Status Register.                                                                                                                                                                                                                                      |

| 24                           | Printer<br>Selected<br>Status                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | SLCT                                                                                                                                                                                                                                                                               | Input. This active high signal is used to tell the COM92C451 that the printer has power on. This signal is bit 4 of the Printer Status Register.                                                                                                                                                                                                                                         |

| 25                           | Error                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | ERROR                                                                                                                                                                                                                                                                              | Input. This active low signal is used to tell the COM92C451 that there is an error condition at the printer. This signal is bit 3 of the Printer Status Register.                                                                                                                                                                                                                        |

| ERFAC                        | E                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                          |

| 36                           | Serial<br>Input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | SIN                                                                                                                                                                                                                                                                                | Input. This signal carries the serial data to the receiver of the COM92C451.                                                                                                                                                                                                                                                                                                             |

| 37                           | Serial<br>Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | SOUT                                                                                                                                                                                                                                                                               | Output. This signal carries the serial data from the transmitter of the COM92C451.                                                                                                                                                                                                                                                                                                       |

| 39                           | Clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | CLK                                                                                                                                                                                                                                                                                | Input. This is the clock input for the COM92C451 Baud Rate Generator.                                                                                                                                                                                                                                                                                                                    |

| 41                           | Output 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | OUT2                                                                                                                                                                                                                                                                               | Output. This signal is a user-designated output which may be programmed by bit 3 of the Modem Control Register. The level of this signal is the inverse of the level programmed into the Modem Control Register.                                                                                                                                                                         |

| 42                           | Request<br>to Send                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | RTS                                                                                                                                                                                                                                                                                | Output. This active low signal is used to tell the modem that the ACE is ready to transmit data.                                                                                                                                                                                                                                                                                         |

| 43                           | Data<br>Terminal<br>Ready                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | DTR                                                                                                                                                                                                                                                                                | Output. This active low signal is used to tell the modem that the ACE is ready to communicate.                                                                                                                                                                                                                                                                                           |

| 44                           | Clear to<br>Send                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | CTS                                                                                                                                                                                                                                                                                | Input. This active low signal is used to tell the COM92C451 that the modem is ready to exchange data. This signal is the complement of bit 4 of the Modem Status Register. Bit 0 of the Modem Status Register may be read to determine whether this signal has changed state since the last reading of the Modem Status Register. CTS has no effect on the transmitter.                  |

| 45                           | <u>Data S</u> et<br>Ready                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | DSR                                                                                                                                                                                                                                                                                | Input. This active low signal is used to tell the COM92C451 that the modem is ready to establish the communication link with it. This signal is the complement of bit 5 of the Modem Status Register. Bit 1 of the Modem Status Register may be read to determine whether this signal has changed stae since the last reading of the Modem Status Register.                              |

| 46                           | Data<br>Carrier<br>Detect                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | DCD                                                                                                                                                                                                                                                                                | Input. This active low signal is used to tell the COM92C451 that the data carrier has been detected by the modem. This signal is the complement of bit 7 of the Modem Status Register. Bit 3 of the Modem Status Register may be read to determine whether this signal has changed state since the last reading of the Modem Status Register. This signal has no effect on the receiver. |

| 47                           | Ring<br>Indicator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | RI                                                                                                                                                                                                                                                                                 | Input. This active low signal is used to tell the COM92C451 that a telephone ringing signal has been received by the modem. This signal is the complement of bit 6 of the Modem Status Register. Bit 2 of the Modem Status Register may be read to determine whether this signal has changed from a low to a high state since the last reading of the Modem Status Register.             |

| 1EOUS                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                          |

| 48                           | Power<br>Supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | VCC                                                                                                                                                                                                                                                                                | +5 Volt Power Supply pin.                                                                                                                                                                                                                                                                                                                                                                |

| 26, 35                       | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | GND                                                                                                                                                                                                                                                                                | Ground pins                                                                                                                                                                                                                                                                                                                                                                              |

|                              | No<br>Connect                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | NC                                                                                                                                                                                                                                                                                 | Make no connection to these pins.                                                                                                                                                                                                                                                                                                                                                        |

|                              | 23   24   25   25   36   37   39   41   42   43   44   45   46   47   EOUS   48   EOUS   48   48   EOUS   EOUS | 23 Paper End  24 Printer Selected Status  25 Error  36 Serial Input  37 Serial Output  39 Clock  41 Output 2  42 Request to Send  43 Data Terminal Ready  44 Clear to Send  45 Data Set Ready  46 Data Carrier Detect  47 Ring Indicator  EFOUS  48 Power Supply  6, 35 Ground  No | Second   PE                                                                                                                                                                                                                                                                                                                                                                              |

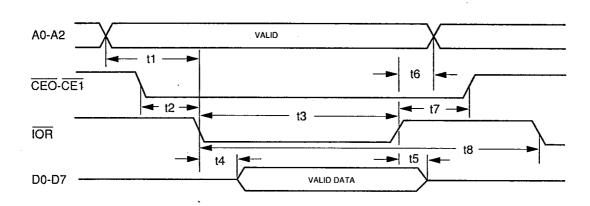

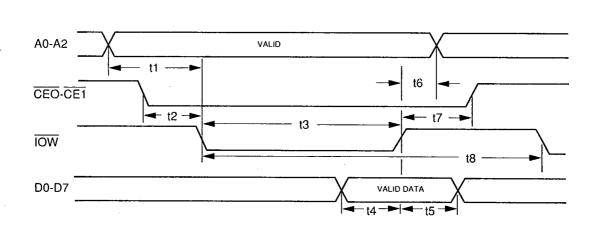

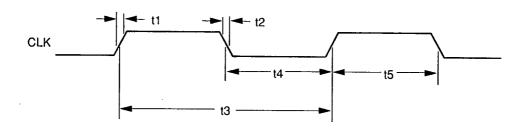

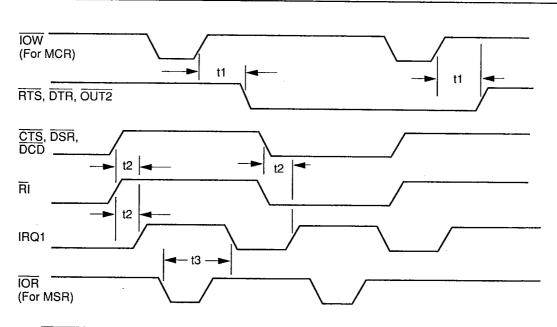

#### SYSTEM DESCRIPTION