# VSC7415 Datasheet 6-Port SGMII Gigabit Ethernet Switch with VeriTime™ and Integrated DPLL and Gigabit Ethernet PHYs

a MICROCHIP company

#### Microsemi Headquarters

One Enterprise, Aliso Viejo, CA 92656 USA Within the USA: +1 (800) 713-4113 Outside the USA: +1 (949) 380-6100 Sales: +1 (949) 380-6136

Fax: +1 (949) 215-4996 Email: sales.support@microsemi.com

www.microsemi.com

©2019 Microsemi, a wholly owned

©2019 Microsemi, a wholly owned subsidiary of Microchip Technology Inc. All rights reserved. Microsemi and the Microsemi logo are registered trademarks of Microsemi Corporation. All other trademarks and service marks are the property of their respective owners.

Microsemi makes no warranty, representation, or guarantee regarding the information contained herein or the suitability of its products and services for any particular purpose, nor does Microsemi assume any liability whatsoever arising out of the application or use of any product or circuit. The products sold hereunder and any other products sold by Microsemi have been subject to limited testing and should not be used in conjunction with mission-critical equipment or applications. Any performance specifications are believed to be reliable but are not verified, and Buyer must conduct and complete all performance and other testing of the products, alone and together with, or installed in, any end-products. Buyer shall not rely on any data and performance specifications or parameters provided by Microsemi. It is the Buyer's responsibility to independently determine suitability of any products and to test and verify the same. The information provided by Microsemi hereunder is provided "as is, where is" and with all faults, and the entire risk associated with such information is entirely with the Buyer. Microsemi does not grant, explicitly or implicitly, to any party any patent rights, licenses, or any other IP rights, whether with regard to such information itself or anything described by such information. Information provided in this document is proprietary to Microsemi, and Microsemi reserves the right to make any changes to the information in this document or to any products and services at any time without notice.

#### **About Microsemi**

Microsemi, a wholly owned subsidiary of Microchip Technology Inc. (Nasdaq: MCHP), offers a comprehensive portfolio of semiconductor and system solutions for aerospace & defense, communications, data center and industrial markets. Products include high-performance and radiation-hardened analog mixed-signal integrated circuits, FPGAs, SoCs and ASICs; power management products; timing and synchronization devices and precise time solutions, setting the world's standard for time; voice processing devices; RF solutions; discrete components; enterprise storage and communication solutions, security technologies and scalable anti-tamper products; Ethernet solutions; Power-over-Ethernet ICs and midspans; as well as custom design capabilities and services. Learn more at www.microsemi.com.

# **Contents**

| 1 | Revisi | on Hist        | tory                                                        | . 1 |

|---|--------|----------------|-------------------------------------------------------------|-----|

|   | 1.1    | Revision       | n 4.1                                                       | . 1 |

|   | 1.2    | Revision       | n 4.0                                                       | . 1 |

|   |        |                |                                                             |     |

| 2 | Produ  | ct Ove         | rview                                                       | 2   |

|   | 2.1    | General        | Features                                                    | . 2 |

|   |        | 2.1.1          | Layer 2 and Layer 3 Forwarding                              |     |

|   |        | 2.1.2          | Timing and Synchronization                                  |     |

|   |        | 2.1.3          | Quality of Service                                          | . 3 |

|   |        | 2.1.4          | Security                                                    | . 3 |

|   |        | 2.1.5          | Management                                                  |     |

|   |        | 2.1.6          | Product Parameters                                          |     |

|   | 2.2    | Applicat       | ions                                                        |     |

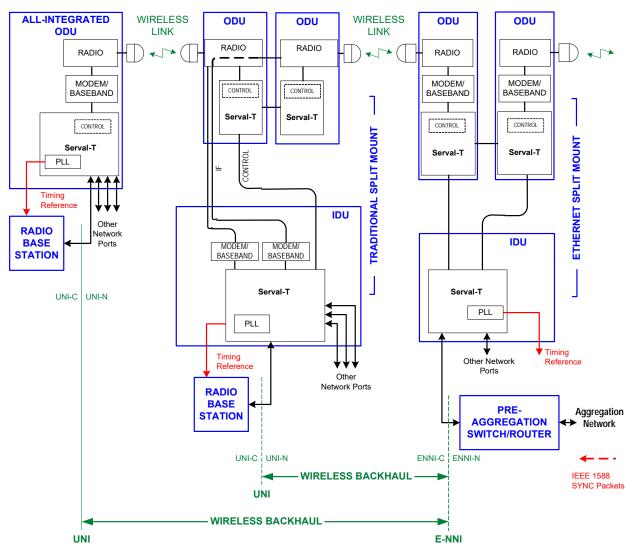

|   |        | 2.2.1          | Wireless Backhaul                                           |     |

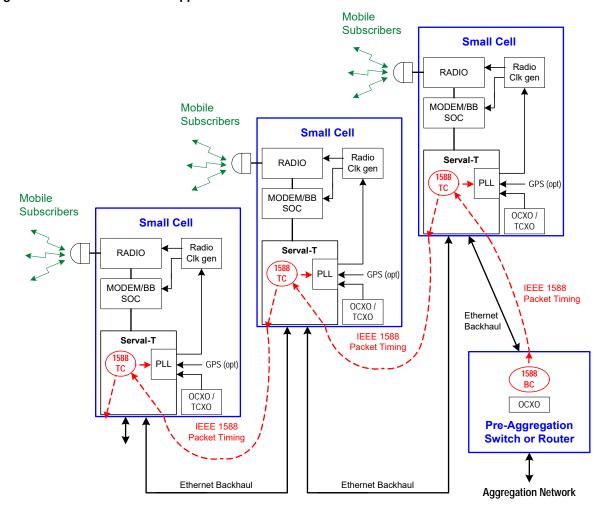

|   |        | 2.2.2          | Small Cell Application                                      | . 7 |

| 3 | Eupoti | onal D         | operintions                                                 | C   |

| 3 |        |                | escriptions                                                 |     |

|   | 3.1    | •              | Notations                                                   |     |

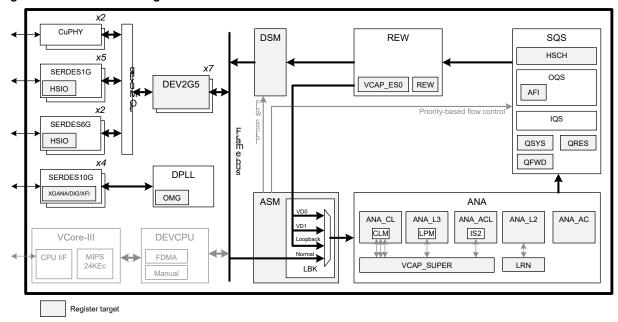

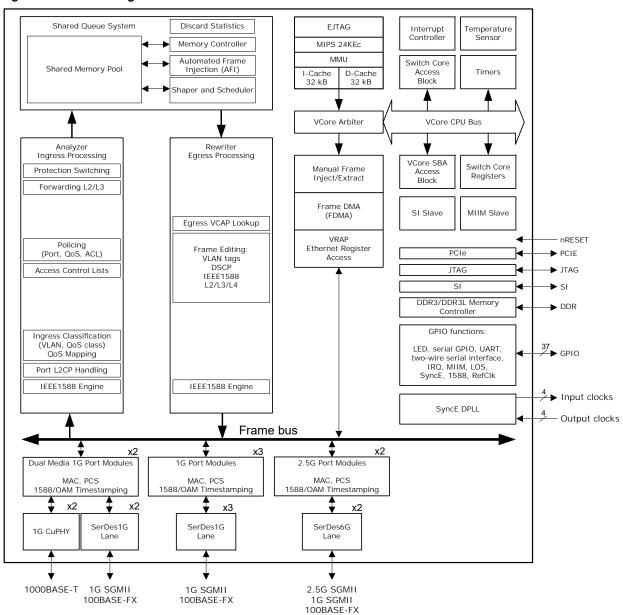

|   | 3.2    |                | nal Overview                                                |     |

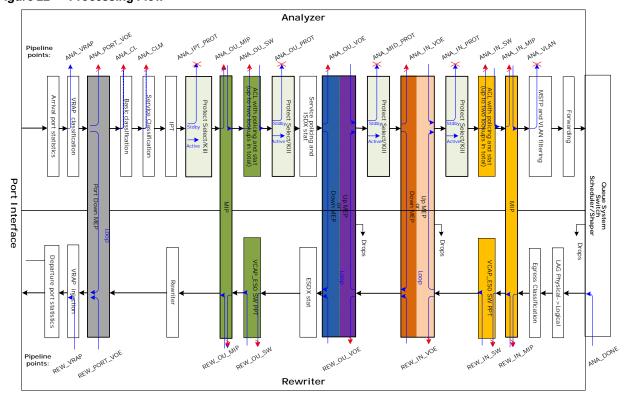

|   |        | 3.2.1          | Frame Arrival in Ports and Port Modules                     |     |

|   |        | 3.2.2          | Basic Classification                                        |     |

|   |        | 3.2.3<br>3.2.4 | Security and Control Protocol Classification                |     |

|   |        | 3.2.4          | Layer 2 Forwarding                                          |     |

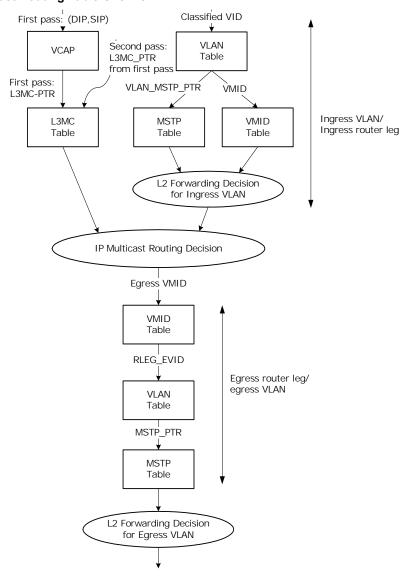

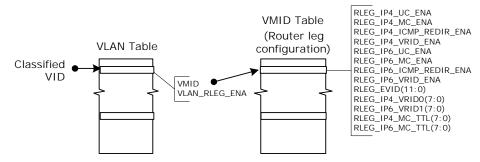

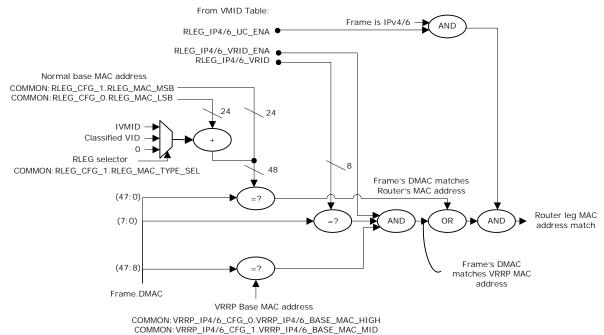

|   |        | 3.2.6          | Layer 3 Forwarding                                          |     |

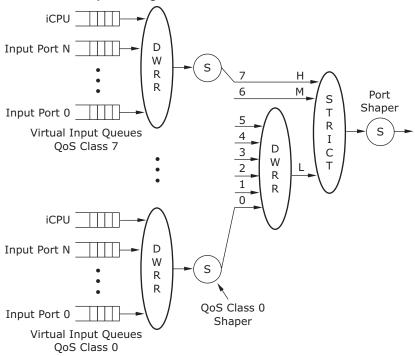

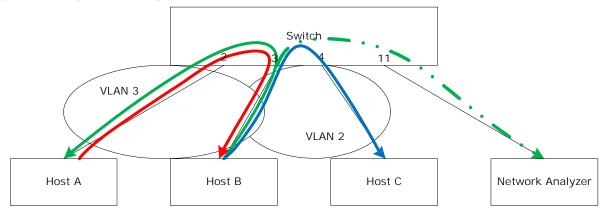

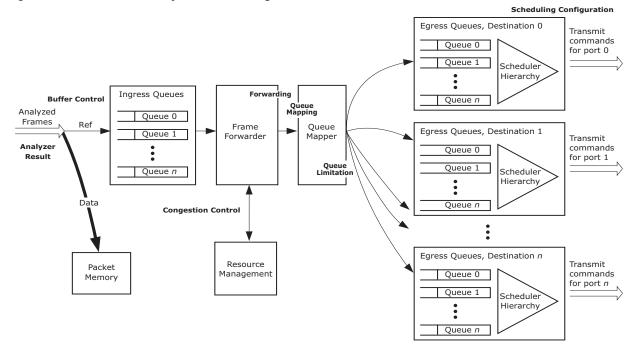

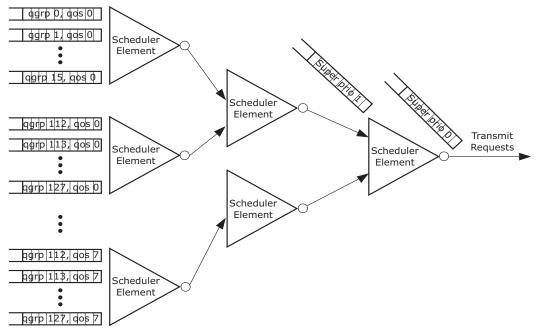

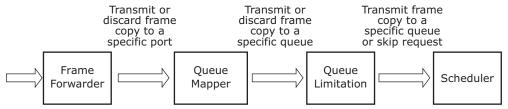

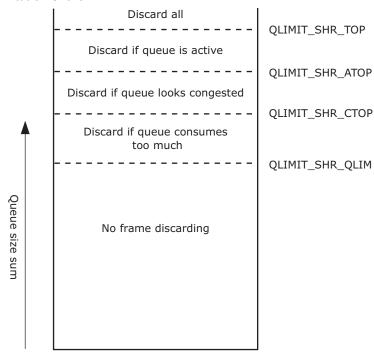

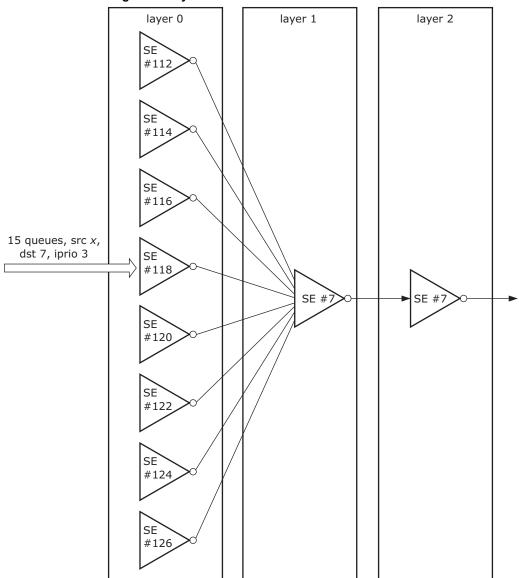

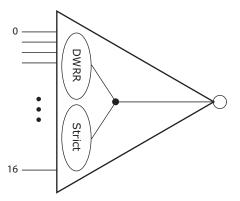

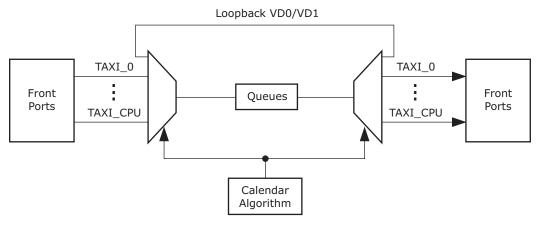

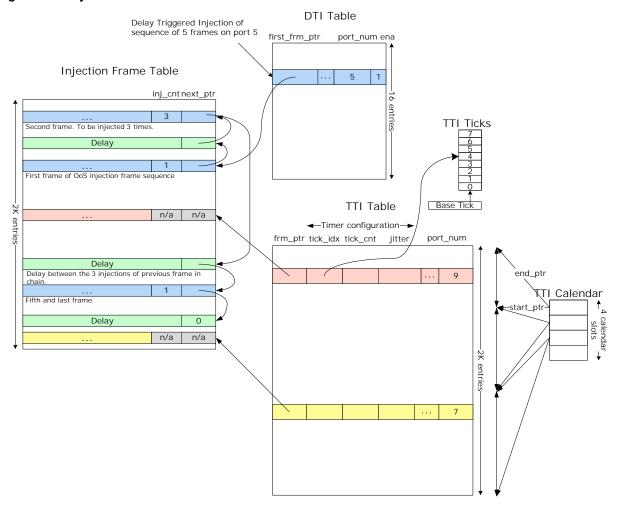

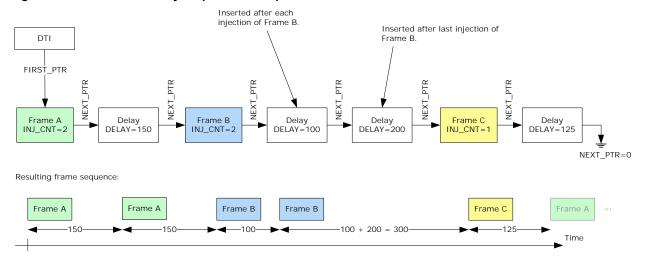

|   |        | 3.2.7          | Shared Queue System and Hierarchical Scheduler              |     |

|   |        | 3.2.8          | Rewriter and Frame Departure                                |     |

|   |        | 3.2.9          | CPU Port Module                                             |     |

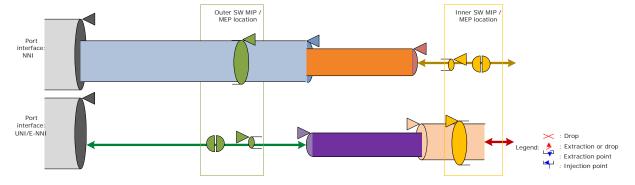

|   |        | 3.2.10         | Synchronous Ethernet and Precision Time Protocol (PTP)      |     |

|   |        | 3.2.11         | CPU Subsystem                                               | 17  |

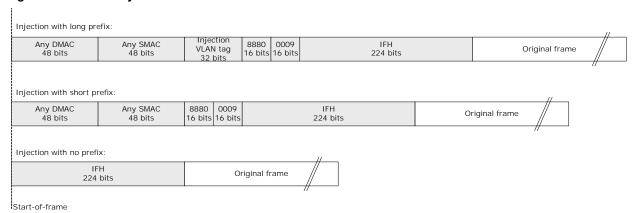

|   | 3.3    | Frame F        | Headers                                                     |     |

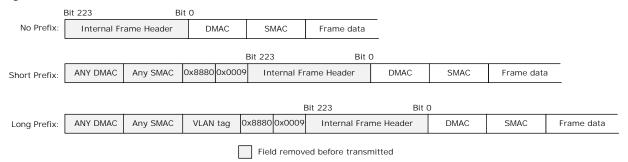

|   |        | 3.3.1          | Internal Frame Header Placement                             |     |

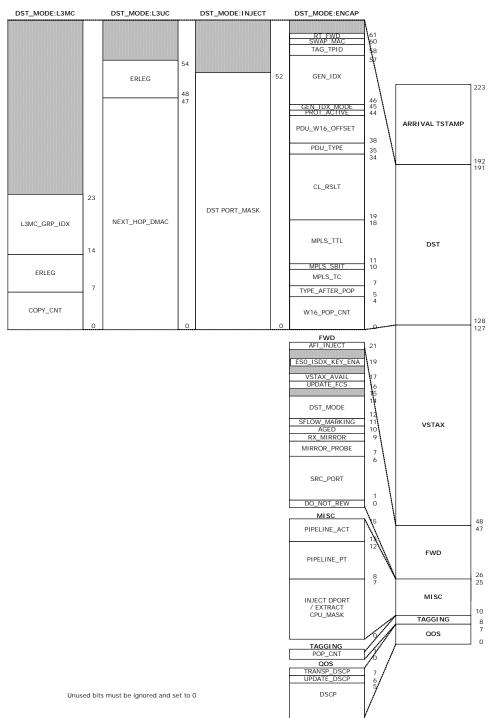

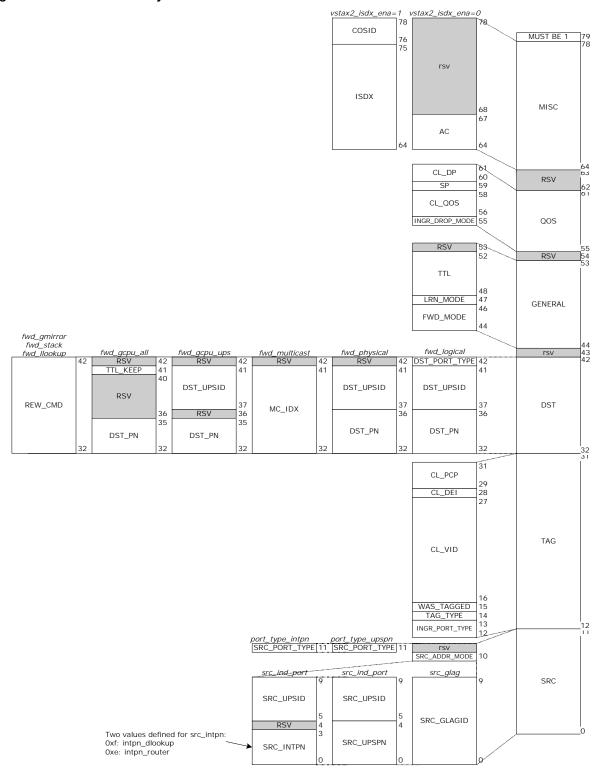

|   |        | 3.3.2          | Internal Frame Header Layout                                |     |

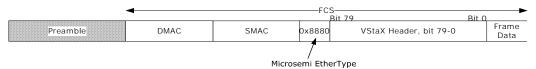

|   |        | 3.3.3          | VStaX Header                                                |     |

|   | 3.4    |                | mbering and Mappings                                        |     |

|   |        | 3.4.1          | Supported SerDes Interfaces                                 |     |

|   |        | 3.4.2<br>3.4.3 | Dual-Media Mode                                             |     |

|   | 2.5    | SERDE:         |                                                             |     |

|   | 3.5    |                |                                                             |     |

|   | 3.6    |                | S6G                                                         |     |

|   | 3.7    |                | Transceivers                                                |     |

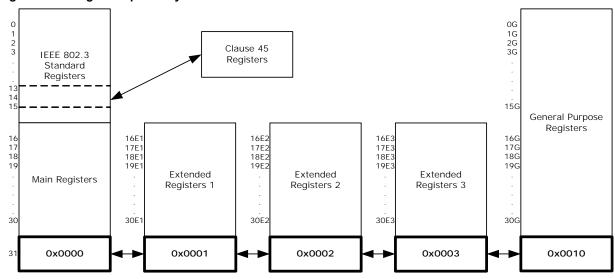

|   |        | 3.7.1<br>3.7.2 | Register Access                                             |     |

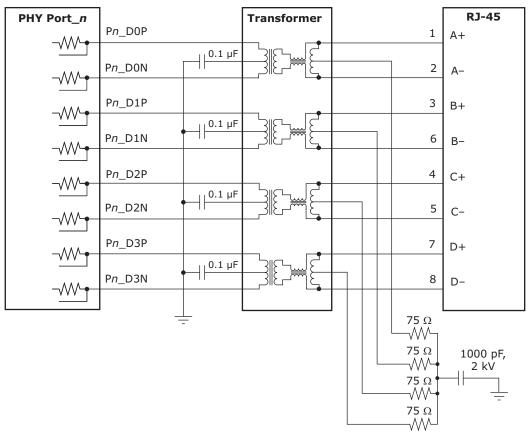

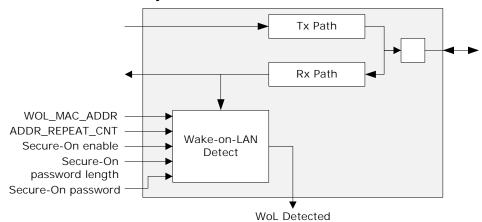

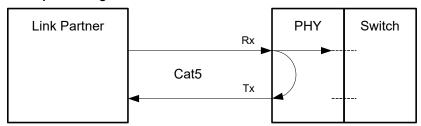

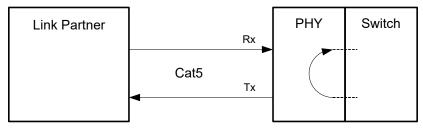

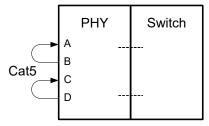

|   |        | 3.7.2          | Cat5 Twisted Pair Media Interface  Wake-On-LAN and SecureOn |     |

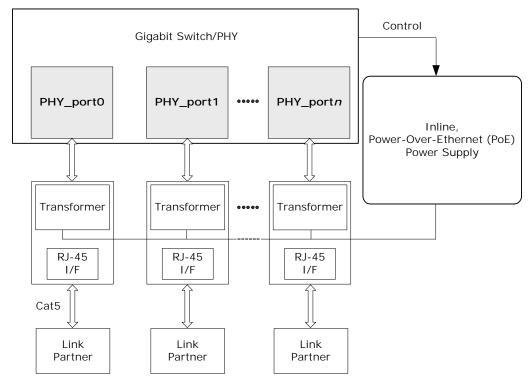

|   |        | 3.7.4          | Ethernet Inline Powered Devices                             |     |

|   |        | 3.7.5          | IEEE 802.3af PoE Support                                    |     |

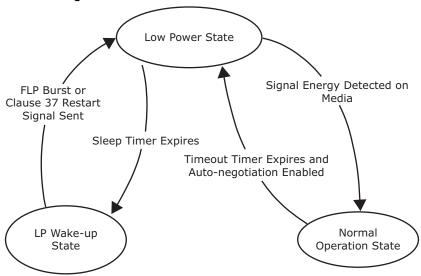

|   |        | 3.7.6          | ActiPHY™ Power Management                                   |     |

|   |        | 3.7.7          | Testing Features                                            |     |

|   |        | 3.7.8          | VeriPHY™ Cable Diagnostics                                  |     |

|   | 3.8    | DEV1G          | and DEV2G5 Port Modules                                     | 36  |

|   |        | 3.8.1          | MAC                                                         |     |

|       | 3.8.2<br>3.8.3<br>3.8.4 | Half-Duplex Mode Physical Coding Sublayer (PCS) Port Statistics | . 41 |

|-------|-------------------------|-----------------------------------------------------------------|------|

| 3.9   |                         | ler                                                             |      |

| 3.9   | 3.9.1                   | Setting Up a Port in the Assembler                              |      |

|       | 3.9.2                   | Setting Up a Port for Frame Injection                           |      |

|       | 3.9.3                   | Setting Up MAC Control Sublayer PAUSE Frame Detection           |      |

|       | 3.9.4                   | Setting Up PFC                                                  |      |

|       | 3.9.5                   | Setting Up Assembler Port Statistics                            |      |

|       | 3.9.6                   | Setting Up the Loopback Path                                    | . 48 |

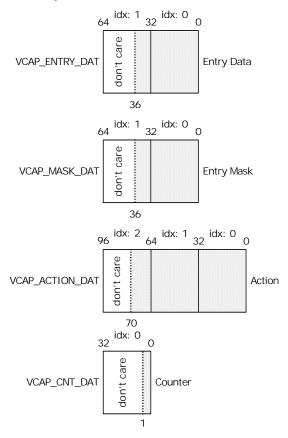

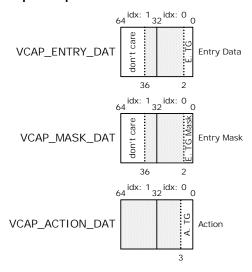

| 3.10  | Versatile               | e Content-Aware Processor (VCAP)                                |      |

|       | 3.10.1                  | Configuring VCAP                                                |      |

|       | 3.10.2                  | Wide VCAP Entries and Actions                                   |      |

|       | 3.10.3                  | Individual VCAPs                                                |      |

|       | 3.10.4                  | VCAP Programming Examples                                       |      |

| 3.11  |                         | Points                                                          |      |

| 0.40  | 3.11.1                  | Pipeline Definitions                                            |      |

| 3.12  | -                       | r                                                               |      |

| 0.40  | 3.12.1                  | Initializing the Analyzer                                       |      |

| 3.13  | 3.13.1                  | LM Keys and Actions                                             |      |

|       | 3.13.1                  | VCAP CLM X1 Key Details                                         |      |

|       | 3.13.2                  | VCAP CLM X1 Key Details                                         |      |

|       | 3.13.4                  | VCAP CLM X4 Key Details                                         |      |

|       | 3.13.5                  | VCAP CLM X8 Key Details                                         |      |

|       | 3.13.6                  | VCAP CLM X16 Key Details                                        | . 82 |

|       | 3.13.7                  | VCAP CLM Actions                                                | . 87 |

| 3.14  | Analyze                 | r Classifier                                                    |      |

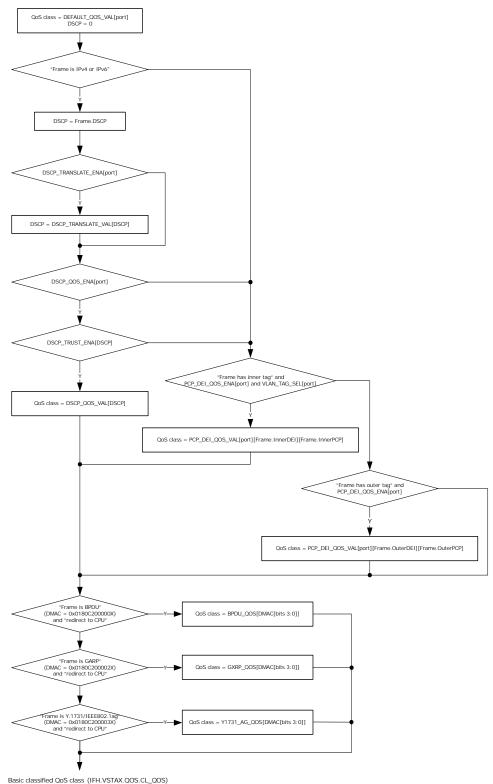

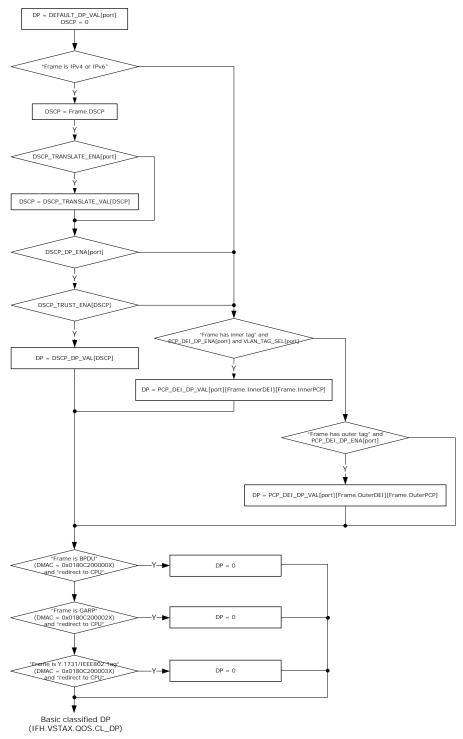

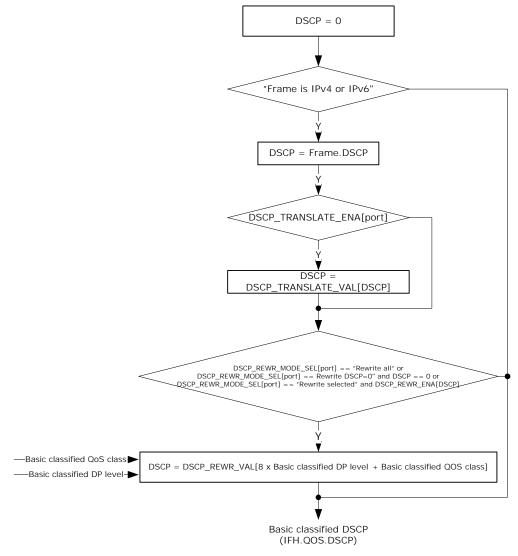

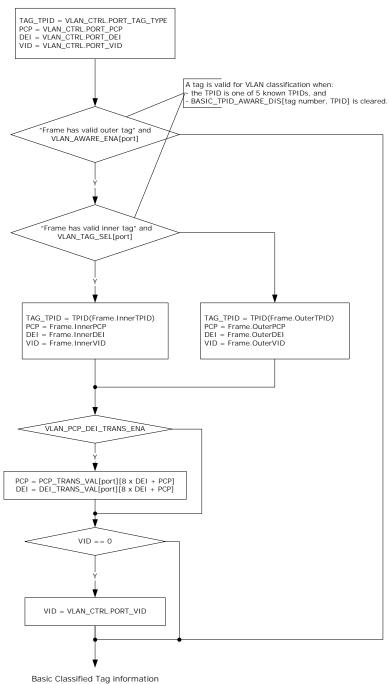

|       | 3.14.1                  | Basic Classifier                                                |      |

|       | 3.14.2                  | VCAP CLM Processing                                             |      |

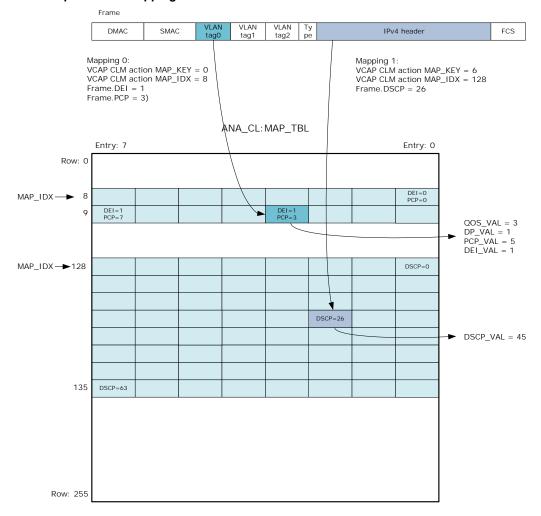

|       | 3.14.3<br>3.14.4        | QoS Mapping Table                                               |      |

| 0.45  |                         | Analyzer Classifier Diagnostics                                 |      |

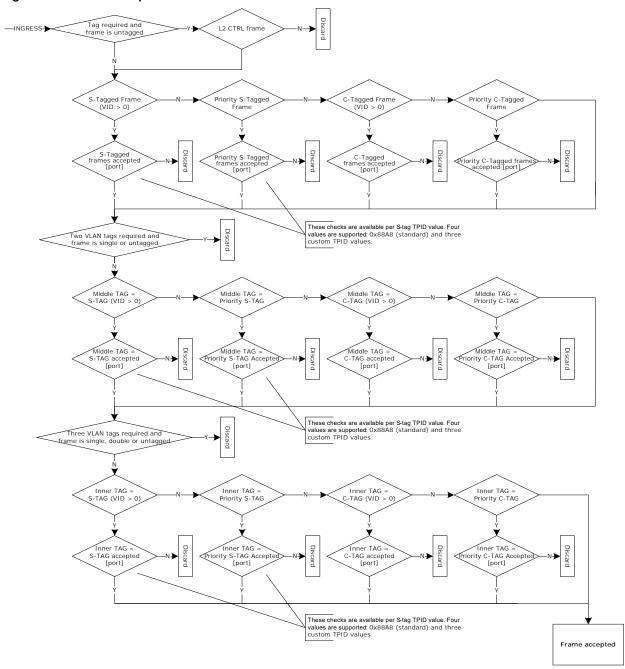

| 3.15  | 3.15.1                  | nd MSTP                                                         |      |

|       | 3.15.1                  | VLAN Pseudo Code                                                |      |

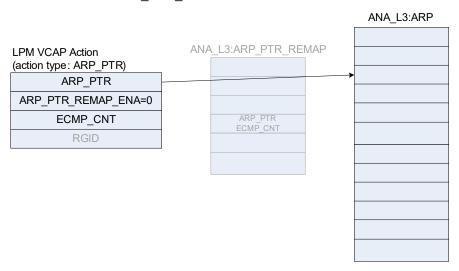

| 3.16  |                         | PM: Keys and Action                                             |      |

| 3.10  | 3.16.1                  | VCAP LPM SGL_IP4 Key Details                                    |      |

|       | 3.16.2                  | VCAP LPM DBL IP4 Key Details                                    |      |

|       | 3.16.3                  | VCAP LPM SGL IP6 Key Details                                    |      |

|       | 3.16.4                  | VCAP LPM DBL_IP6 Key Details                                    | 127  |

|       | 3.16.5                  | VCAP LPM Actions                                                | 127  |

| 3.17  | IP Proce                | essing                                                          | 129  |

|       | 3.17.1                  | IP Source/Destination Guard                                     |      |

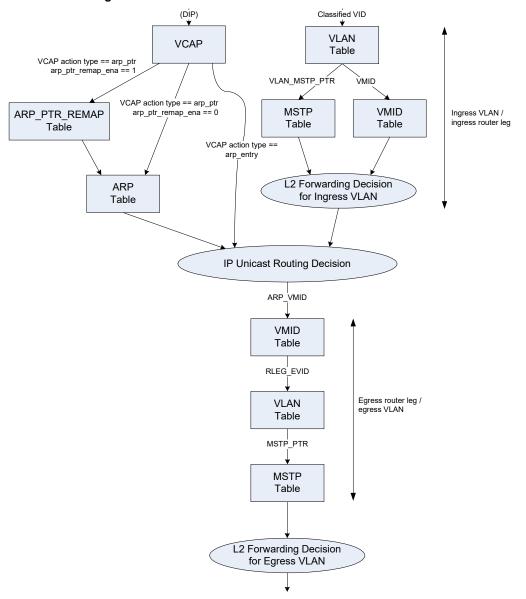

|       | 3.17.2                  | IP Routing                                                      |      |

|       | 3.17.3                  | Statistics                                                      |      |

| 0.40  | 3.17.4                  | IGMP/MLD Snooping Switch                                        |      |

| 3.18  | 3.18.1                  | S2 Keys and Actions                                             |      |

|       | 3.18.2                  | VCAP IS2 Keys                                                   |      |

| 3.19  |                         | r Access Control Lists                                          |      |

| J. 13 | 3.19.1                  | VCAP IS2                                                        |      |

|       | 3.19.2                  | Analyzer Access Control List Frame Rewriting                    |      |

| 3.20  |                         | r Layer 2 Forwarding and Learning                               |      |

|       | 3.20.1                  | Analyzer MAC Table                                              |      |

|       | 3.20.2                  | MAC Table Updates                                               |      |

|       | 3.20.3                  | CPU Access to MAC Table                                         | 167  |

|   |   | IVIICI   | USCIII    | 1 |

|---|---|----------|-----------|---|

| 3 | M | Місвосні | p company |   |

|                                                                                                                                                                                                            | SCAN Command                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

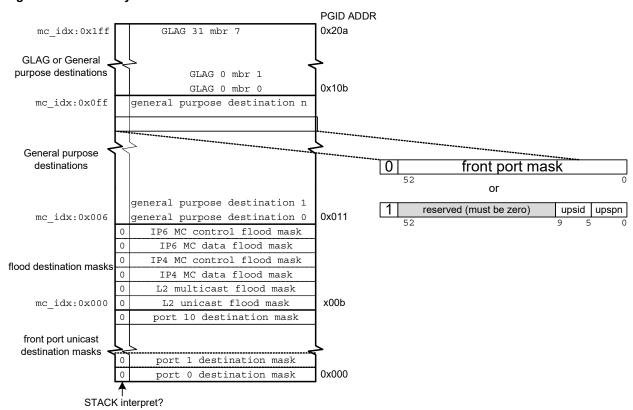

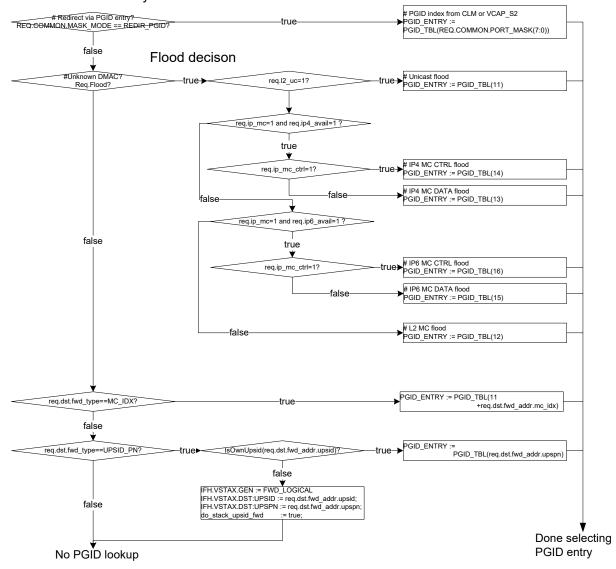

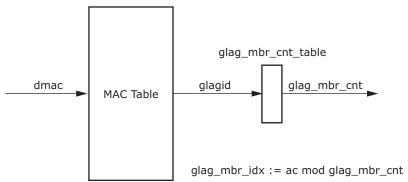

| 3.20.5                                                                                                                                                                                                     | Forwarding Lookups                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

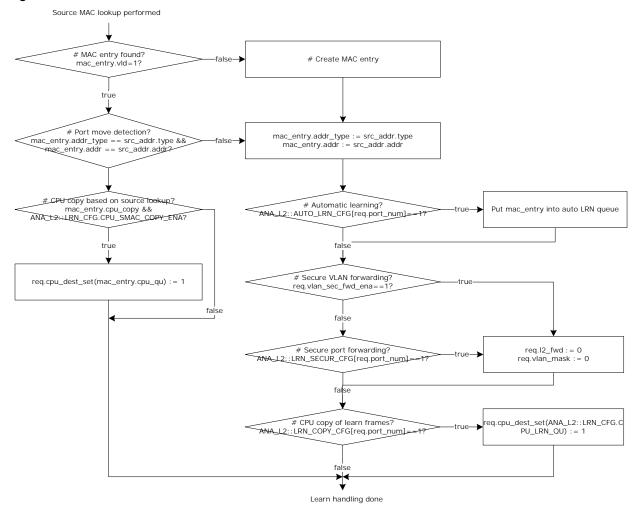

| 3.20.6                                                                                                                                                                                                     | Source Check and Automated Learning                                                                                                                                                                                                                                                                                                                                                                          | . 175                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 3.20.7                                                                                                                                                                                                     | Automated Aging (AUTOAGE)                                                                                                                                                                                                                                                                                                                                                                                    | . 178                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 3.20.8                                                                                                                                                                                                     | Interrupt Handling                                                                                                                                                                                                                                                                                                                                                                                           | . 179                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Analyze                                                                                                                                                                                                    | r Access Control Forwarding, Policing, and Statistics                                                                                                                                                                                                                                                                                                                                                        | . 180                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| -                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                                                                                                                                                            | <del>-</del>                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                                                                                                                                                            | · · · · · · · · · · · · · · · · · · ·                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |