# CMOS Micro Program Sequencers

#### **Features**

- Fast

- CY7C909/11 has a 30-ns (min.) clock-to-output cycle time (commercial and military)

- Low power

- I<sub>CC</sub> (max.) = 55 mA (commercial and military)

- V<sub>CC</sub> margin

- -5V ±10%

- All parameters guaranteed over commercial and military operating temperature range

- Infinitely expandable in 4-bit increments

- Capable of withstanding >2001V static discharge voltage

- Pin compatible and functionally equivalent to Am2909A/Am2911A

## **Functional Description**

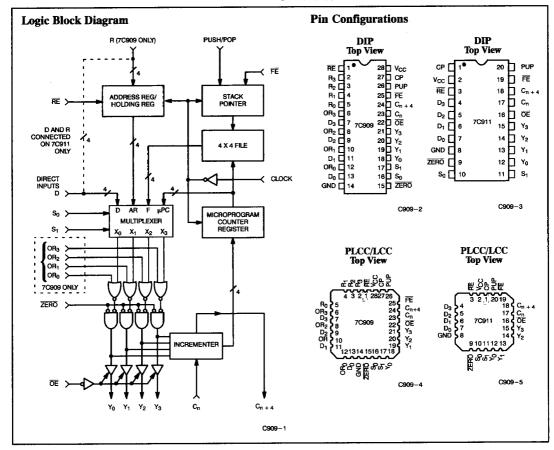

The CY7C909 and CY7C911 are high-speed, four-bit-wide address sequencers intended to control the sequence of execution of micro-instructions contained in microprogram memory. They may be connected in parallel to expand the address width in 4-bit increments. Both devices are implemented in high-performance CMOS for optimum speed and power.

The CY7C909 can select an address from any of four sources. They are: (1) a set of four external direct inputs (D<sub>i</sub>); (2) exter-

nal data stored in an internal register  $(R_i)$ ; (3) a four-word-deep push/pop stack; or (4) a program counter register (which usually contains the last address plus one). The push/pop stack includes control lines so that it can efficiently execute nested subroutine linkages. In the CY7C909, each of the four outputs  $(Y_i)$  can be ORed with an external input for conditional skip or branch instructions. A  $\overline{ZERO}$  input line forces the outputs to all zeros. The outputs are three-state, controlled by the output enable  $(\overline{OE})$  input.

The CY7C911 is an identical circuit to the CY7C909, except the four OR inputs are removed and the D and R inputs are tied together. The CY7C911 is available in a 20-pin, 300-mil package.

## **Maximum Ratings**

| (Above which the useful life may be impaired. For user guidelines, not tested.) |

|---------------------------------------------------------------------------------|

| Storage Temperature $\  \  \  \  \  \  \  \  \  \  \  \  \ $                    |

| eq:ambient Temperature with Power Applied                                       |

| Supply Voltage to Ground Potential 0.5V to +7.0V                                |

| DC Voltage Applied to Outputs in High Z State $$ - 0.5V to +7.0V                |

| DC Input Voltage 3.0V to +7.0V                                                  |

| Output Current, into Outputs (LOW)                                              |

| Static Discharge Voltage(per MIL-STD-883, Method 3015) | >2001V  |

|--------------------------------------------------------|---------|

| Latch-Up Current                                       | >200 mA |

## **Operating Range**

| Range                   | Ambient<br>Temperature | v <sub>cc</sub> |

|-------------------------|------------------------|-----------------|

| Commercial              | 0°C to + 70°C          | 5V ±10%         |

| Military <sup>[1]</sup> | - 55°C to +125°C       | 5V ±10%         |

## Electrical Characteristics Over the Operating Range<sup>[2]</sup>

| Parameters       | Description                              | Test Conditions                                                        | Test Conditions |      |      |    |

|------------------|------------------------------------------|------------------------------------------------------------------------|-----------------|------|------|----|

| V <sub>OH</sub>  | Output HIGH Voltage                      | $V_{\rm CC}$ = Min., $I_{\rm OH}$ = $-2.6$ mA                          | 2.4             |      | V    |    |

|                  |                                          | $V_{\rm CC} = \text{Min.}, I_{\rm OH} = -1.0 \text{mA}$                | Military        | 2.4  |      | V  |

| V <sub>OL</sub>  | Output LOW Voltage                       | $V_{CC} = Min., I_{OL} = 16.0 \text{ mA}$                              |                 |      | 0.4  | V  |

| V <sub>IH</sub>  | Input HIGH Voltage                       |                                                                        |                 |      |      |    |

| V <sub>IL</sub>  | Input LOW Voltage                        |                                                                        | - 2.0           | 0.8  | V    |    |

| I <sub>IX</sub>  | Input Load Current                       | $GND \leq V_I \leq V_{CC}$                                             | - 10            | +10  | μΑ   |    |

| I <sub>OZ</sub>  | Output Leakage Current                   | $GND \le V_O \le V_{CC}$ , Output Disa                                 | abled           | - 20 | +20  | μА |

| I <sub>OS</sub>  | Output Short Circuit Current[3]          | $V_{CC} = Max., V_{OUT} = GND \text{ or } Y_{CC}$                      | $v_{cc}$        | - 30 | - 85 | mA |

| $I_{CC}$         | V <sub>CC</sub> Operating Supply Current | $V_{CC} = Max., I_{OUT} = 0 mA$                                        | Commercial      |      | 55   | mA |

|                  |                                          |                                                                        | Military        |      | 55   |    |

| I <sub>CC1</sub> | V <sub>CC</sub> Operating Supply Current | $V_{CC} = Max.$ Commercial $V_{IH} \ge 3.0V, V_{IL} \le 0.4V$ Military |                 |      | 35   | mA |

|                  |                                          | $V_{IH} \ge 3.0V$ , $V_{IL} \le 0.4V$                                  | Military        | 1    | 35   |    |

## Capacitance<sup>[4]</sup>

| Parameters       | Description        | Test Conditions             | Max. | Units |  |

|------------------|--------------------|-----------------------------|------|-------|--|

| C <sub>IN</sub>  | InputCapacitance   | $T_A = 25$ °C, $f = 1$ MHz, | 5    | pF    |  |

| C <sub>OUT</sub> | Output Capacitance | $\dot{V}_{CC} = 5.0\dot{V}$ | 7    | pF    |  |

## Notes:

- 1. T<sub>A</sub> is the "instant on" case temperature.

- See the last page of this specification for Group A subgroup testing information.

- 3. Not more than 1 output should be shorted at one time. Duration of the short circuit should not exceed 30 seconds.

- Tested initially and after any design or process changes that may affect these parameters.

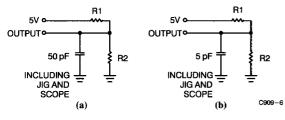

## **AC Test Loads and Waveforms**

|    | Commercial | Military |

|----|------------|----------|

| R1 | 254Ω       | 258Ω     |

| R2 | 187Ω       | 216Ω     |

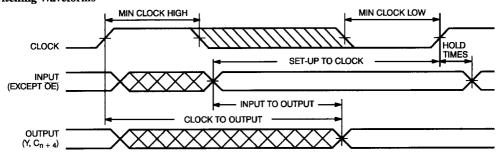

## Switching Characteristics Over the Operating Range [2, 5]

|                                                  | CY7        | /C909-30         | CY7C911      | -30              | CY7C909-40, CY7C911-40 |                  |          |                    |       |

|--------------------------------------------------|------------|------------------|--------------|------------------|------------------------|------------------|----------|--------------------|-------|

|                                                  | Comn       | nercial          | Mili         | itary            | Comn                   | nercial          | Military |                    | Units |

| Minimum Clock LOW Time <sup>[6]</sup>            | 1          | 5                | 1            | 15               |                        | 20               |          | 0                  | ns    |

| Minimum Clock HIGH Time <sup>[6]</sup>           | 1          | 5                | 15           |                  | 2                      | 0                | 2        | 0                  | ns    |

| MAXIMUM COMBINATORIALI                           | PROPAGAT   | ION DELA         | YS           |                  |                        |                  |          |                    |       |

| From Input To:                                   | Y          | C <sub>n+4</sub> | Y            | C <sub>n+4</sub> | Y                      | C <sub>n+4</sub> | Y        | C <sub>n + 4</sub> | ns    |

| D <sub>i</sub>                                   | 17         | 18               | 18           | 19               | 17                     | 22               | 20       | 25                 | ns    |

| S <sub>0</sub> , S <sub>1</sub>                  | 18         | 18               | 20           | 20               | 29                     | 34               | 29       | 34                 | ns    |

| OR <sub>i</sub> (CY7C909)                        | 16         | 16               | 17           | 17               | 17                     | 22               | 20       | 25                 | ns    |

| C <sub>n</sub>                                   | T -        | 13               | _            | 15               |                        | 14               | _        | 16                 | ns    |

| ZERO                                             | 18         | 18               | 20           | 20               | 29                     | 34               | 30       | 35                 | ns    |

| OE LOW to Output                                 | 16         | _                | 18           | _                | 25                     | _                | 25       | _                  | ns    |

| OE HIGH to High Z <sup>[5]</sup>                 | 16         | -                | 18           | <u> </u>         | 25                     |                  | 25       | _                  | ns    |

| Clock HIGH, $S_1$ , $S_0 = LH$                   | 20         | 20               | 22           | 22               | 39                     | 44               | 45       | 50                 | ns    |

| Clock HIGH, $S_1$ , $S_0 = LL$                   | 20         | 20               | 22           | 22               | 39                     | 44               | 45       | 50                 | ns    |

| Clock HIGH, S <sub>1</sub> S <sub>0</sub> , = HL | 20         | 20               | 22           | 22               | 44                     | 49               | 53       | 58                 | ns    |

| MINIMUM SET-UPAND HOLD                           | TIMES (All | Times Rel        | ative to Clo | ck LOW-t         | to-HIGH T              | ransition)       |          |                    |       |

| From Input                                       | Set-Up     | Hold             | Set-Up       | Hold             | Set-Up                 | Hold             | Set-Up   | Hold               |       |

| RE                                               | 11         | 0                | 12           | 0                | 19                     | 0                | 19       | 0                  | ns    |

| $R_{i}^{[7]}$                                    | 10         | 0                | 11           | 0                | 10                     | 0                | 12       | 0                  | ns    |

| Push/Pop                                         | 12         | 0                | 13           | 0                | 25                     | 0                | 27       | 0                  | ns    |

| FE                                               | 12         | 0                | 13           | 0                | 25                     | 0                | 27       | 0                  | ns    |

| Cn                                               | 10         | 0                | 11           | 0                | 18                     | 0                | 18       | 0                  | ns    |

| D <sub>i</sub>                                   | 14         | 0                | 16           | 0                | 25                     | 0                | 25       | 0                  | ns    |

| OR <sub>i</sub> (CY7C909)                        | 12         | 0                | 14           | 0                | 25                     | 0                | 25       | 0                  | ns    |

| S <sub>0</sub> , S <sub>1</sub>                  | 14         | 0                | 16           | 0                | 25                     | 0                | 29       | 0                  | ns    |

| ZERO                                             | 12         | 0                | 13           | 0                | 25                     | 0                | 29       | 0                  | ns    |

$R_i$  and  $D_i$  are internally connected on the CY7C911. Use  $R_i$  set-up and hold times for Di inputs.

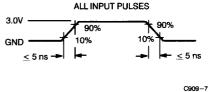

## **Switching Waveforms**

C909-8

Notes: 5. Ot

Output loading as in part (b) of AC Test Loads and Waveforms.

System clock cycle time (Clock LOW Time and Clock HIGH Time) cannot be less than maximum propagation delay.

## Functional Description (continued)

The tables below define the control logic of the 7C909/911. Table 1 contains the multiplexer control logic, which selects the address source to appear on the outputs.

**Table 1. Address Source Selection**

| Octal | S <sub>1</sub> | S <sub>0</sub> | Source for Y Outputs        |

|-------|----------------|----------------|-----------------------------|

| 0     | L              | L              | Microprogram Counter (μPC)  |

| 1     | L              | Н              | Address/HoldingRegister(AR) |

| 2     | H              | L              | Push-Pop Stack (STK)        |

| Z     | H              | Н              | Direct inputs (Di)          |

Control of the Push/Pop Stack is contained in *Table 2*. File enable (FE) enables stack operations, while Push/Pop (PUP) controls the stack.

**Table 2. Synchronous Stack Control**

| FE | PUP | Push-Pop Stack Change                               |

|----|-----|-----------------------------------------------------|

| Н  | X   | Nochange                                            |

| Ĺ  | Н   | Push current PC into stack, increment stack pointer |

| L  | L   | Pop stack, decrement stack pointer                  |

<u>Table 3</u> illustrates the output control logic of the 7C909/911. The  $\overline{\text{ZERO}}$  control forces the outputs to zero. The OR inputs are ORed with the output of the multiplexer.

**Table 3. Output Control**

| ORi | ZERO | ŌĒ | Yi                                               |

|-----|------|----|--------------------------------------------------|

| X   | X    | Н  | High Z                                           |

| X   | L    | L  | L                                                |

| Н   | Н    | L  | Н                                                |

| L   | Н    | L  | Source selected by S <sub>0</sub> S <sub>1</sub> |

Table 4 defines the effect of  $S_0$ ,  $S_1$ ,  $\overline{FE}$ , and PUP control signals on the 7C909. It illustrates the address source on the outputs and the contents of the internal registers for every combination of these signals. The internal register contents are illustrated before and after the clock LOW-to-HIGH edge.

**Table 4. Output Control**

| Cycle | $S_1, S_0, \overline{FE}, PUP$ | μPC    | REG | STK0 | STK1 | STK2 | STK3 | Yout | Comment                  | Principle<br>Use |

|-------|--------------------------------|--------|-----|------|------|------|------|------|--------------------------|------------------|

| N     | 0000                           | J      | K   | Ra   | Rb   | Rc   | Rd   | J    | Pop Stack                | End Loop         |

| N + 1 | _                              | J + 1  | K   | Rb   | Rc   | Rd   | Ra   | _    |                          |                  |

| N     | 0001                           | J      | K   | Ra   | Rb   | Rc   | Rd   | J    | Push μPC                 | Set-Up           |

| N + 1 | _                              | J + 1  | K   | J    | Ra   | Rb   | Rc   | _    |                          | Loop             |

| N     | 001X                           | J      | K   | Ra   | Rb   | Rc   | Rd   | J    | Continue                 | Continue         |

| N + 1 | _                              | J + 1  | K   | Ra   | Rb   | Rc   | Rd   | _    |                          |                  |

| N     | 0100                           | J      | K   | Ra   | Rb   | Rc   | Rd   | K    | Use AR for Address;      | End Loop         |

| N + 1 | _                              | K + 1  | K   | Rb   | Rc   | Rd   | Ra   |      | Pop Stack                |                  |

| N     | 0101                           | J      | K   | Ra   | Rb   | Rc   | Rd   | K    | Jump to Address in AR;   | JSR AR           |

| N + 1 |                                | K + 1  | K   | J    | Ra   | Rb   | Rc   | -    | Push μPC                 |                  |

| N     | 011X                           | J      | K   | Ra   | Rb   | Rc   | Rd   | K    | Jump to Address in AR    | JMPAR            |

| N + 1 | _                              | K + 1  | K   | Ra   | Rb   | Rc   | Rd   | _    |                          | •                |

| N     | 1000                           | J      | K   | Ra   | Rb   | Rc   | Rd   | Ra   | Jump to Address in STK0; | RTS              |

| N + 1 | _                              | Ra + 1 | K   | Rb   | Rc   | Rd   | Ra   | _    | Pop Stack                |                  |

| N     | 1001                           | J      | K   | Ra   | Rb   | Rc   | Rd   | Ra   | Jump to Address in STK0; |                  |

| N + 1 | _                              | Ra + 1 | K   | J    | Ra   | Rb   | Rc   | _    | Push μPC                 |                  |

| N     | 101X                           | J      | K   | Ra   | Rb   | Rc   | Rd   | Ra   | Jump to Address in STK0  | Stack Ref        |

| N + 1 | _                              | Ra + 1 | K   | Ra   | Rb   | Rc   | Rd   | -    |                          | (Loop)           |

| N     | 1100                           | J      | K   | Ra   | Rb   | Rc   | Rd   | D    | Jump to Address on D;    | End Loop         |

| N + 1 | _                              | D + 1  | K   | Rb   | Rc   | Rd   | Ra   |      | Pop Stack                |                  |

| N     | 1101                           | J      | K   | Ra   | Rb   | Rc   | Rd   | D    | Jump to Address on D;    | JSR D            |

| N + 1 | _                              | D + 1  | K   | J    | Ra   | Rb   | Rc   | _    | Push μPC                 |                  |

| N     | 111X                           | J      | K   | Ra   | Rb   | Rc   | Rd   | D    | Jump to Address on D     | JMP D            |

| N + 1 | _                              | D + 1  | K   | Ra   | Rb   | Rc   | Rd   | _    |                          |                  |

J = Contents of microprogram counter; K = Contents of address register; Ra, Rb, Rc, Rd = Contents in stack

## Functional Description (continued)

Two examples of subroutine execution appear below. Table 5 illustrates a single subroutine while Tables 6 illustrates two nested subroutines. The starting address of the subroutine is applied to the D inputs of the 7C909 at the appropriate time, and the instruction to be performed is applied to the S<sub>0.1</sub>, FE, and PUP inputs. Typically, these signals are derived from a micro-instruction, register, and the output of the sequencer (Y<sub>1</sub>) that is the address in the control ROM of the next micro-instruction to be executed.

Tables 5 shows the sequence of micro-instructions to be executed. At address J+2, the sequence control portion of the micro-instruction contains the command "Jump to subroutine at A." At the time  $T_2$ , the 7C909 inputs are set up to execute the jump and save the return address. The subroutine address A is applied to the D inputs and appears on the Y outputs. On the next clock transition, the return address J+3 is pushed onto the stack. The return instruction is executed at  $T_5$ . Tables 6 has a similar timing chart showing one subroutine linking to a second, with the latter consisting of only one micro-instruction.

Table 5. Subroutine Execution<sup>[8]</sup>

| Execute Cycl               | ie                                                | T₀                      | T <sub>1</sub>          | T <sub>2</sub>          | T <sub>3</sub>            | T <sub>4</sub>                | T <sub>5</sub>                | T <sub>6</sub>          | T <sub>7</sub>     |

|----------------------------|---------------------------------------------------|-------------------------|-------------------------|-------------------------|---------------------------|-------------------------------|-------------------------------|-------------------------|--------------------|

| Signals                    | Clock                                             |                         |                         |                         |                           |                               |                               |                         |                    |

| Inputs                     | S <sub>1</sub> , S <sub>0</sub><br>FE<br>PUP<br>D | 0<br>H<br>X<br>X        | 0<br>H<br>X<br>X        | 3<br>L<br>H<br>A        | 0<br>H<br>X<br>X          | 0<br>H<br>X<br>X              | 2<br>L<br>L<br>X              | 0<br>H<br>X<br>X        | 0<br>H<br>X<br>X   |

| Internal<br>Registers      | μPC<br>STK0<br>STK1<br>STK2<br>STK3               | J+1<br>-<br>-<br>-<br>- | J+2<br>-<br>-<br>-<br>- | J+3<br>-<br>-<br>-<br>- | A+1<br>J+3<br>-<br>-<br>- | A + 2<br>J + 3<br>-<br>-<br>- | A + 3<br>J + 3<br>-<br>-<br>- | J+4<br>-<br>-<br>-<br>- | J+5<br>-<br>-<br>- |

| Output                     | Y                                                 | J + 1                   | J + 2                   | Α                       | A + 1                     | A + 2                         | J + 3                         | J+4                     | J + 5              |

| Instruction being executed |                                                   | Continue                | Continue                | JSR A                   | Continue                  | Continue                      | RTS                           | Continue                | Continue           |

Table 6. Two Nested Subroutines, Routine B is Only One Instruction[8]

| Execute C                        | ycle                                              | T⊕                      | T <sub>1</sub>            | T <sub>2</sub>       | T <sub>3</sub>                | T <sub>4</sub>                | T <sub>5</sub>         | T <sub>6</sub>    | T <sub>7</sub>                | T <sub>8</sub>                | T <sub>9</sub>          |

|----------------------------------|---------------------------------------------------|-------------------------|---------------------------|----------------------|-------------------------------|-------------------------------|------------------------|-------------------|-------------------------------|-------------------------------|-------------------------|

| Signals                          | Clock                                             |                         |                           |                      |                               |                               |                        |                   |                               |                               |                         |

| Inputs<br>(from<br>µWR)          | S <sub>1</sub> , S <sub>0</sub><br>FE<br>PUP<br>D | 0<br>H<br>X<br>X        | 3<br>L<br>H<br>A          | 0<br>H<br>X<br>X     | 0<br>H<br>X<br>X              | 3<br>L<br>H<br>B              | 0<br>H<br>X<br>X       | L<br>L<br>X       | 0<br>H<br>X<br>X              | L<br>L<br>X                   | 0<br>H<br>X<br>X        |

| Internal<br>Registers            | μPC<br>STK0<br>STK1<br>STK2<br>STK3               | J+2<br>-<br>-<br>-<br>- | J + 2<br>-<br>-<br>-<br>- | A+1<br>J+2<br>-<br>- | A + 2<br>J + 2<br>-<br>-<br>- | A + 3<br>J + 2<br>-<br>-<br>- | B+1<br>A+3<br>J+2<br>- | B+1<br>A+3<br>J+2 | A + 4<br>J + 2<br>-<br>-<br>- | A + 5<br>J + 2<br>-<br>-<br>- | J+3<br>-<br>-<br>-<br>- |

| Output                           | Y                                                 | J+1                     | Α                         | A + 1                | A + 2                         | В                             | B +1                   | A + 3             | A + 4                         | J+3                           | J+4                     |

| Instruction<br>being<br>executed |                                                   | Continue                | JSR A                     | Continue             | Continue                      | JSR B                         | Continue               | RTS               | Continue                      | RTS                           | Continue                |

Note:

8.  $C_n = HIGH$

C909-9

Note:

Ri and Di connected together and ORi inputs removed on CY7C911.

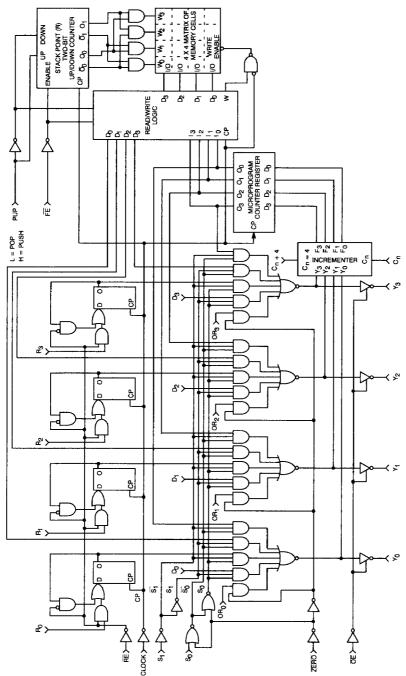

Figure 1. Microprocessor Sequencer Block Diagram

## Functional Description (continued)

#### Architecture

The CY7C909 and CY7C911 are CMOS microprogram sequencers for use in high-speed processor applications. They are cascadable in 4-bit increments. Two devices can address 256 words of microprogram, three can address up to 4K words, and so on. The architecture of the CY7C909/911 is illustrated in the logic diagram in Figure 1. The various blocks are described below.

#### Multiplexer

The multiplexer is controlled by the  $S_0$  and  $S_1$  inputs to select the address source. It selects either the direct inputs  $(D_i)$ , the address register (AR), the microprogram counter ( $\mu$ PC), or the stack (SP) as the source of the next micro-instruction address.

#### **Direct Inputs**

The direct inputs (D<sub>i</sub>) allow addresses from an external source to be output on the Y outputs. On the CY7C911, the direct inputs are also inputs to the address register.

#### Address Register

The address register (AR) consists of four D-type, edge-triggered, flip-flops that are controlled by the register enable (RE) input. When register enable is LOW, new data is entered into the register on the LOW-to-HIGH clock transition.

## Microprogram Counter

The microprogram counter ( $\mu$ PC) is composed of a 4-bit incrementer followed by a 4-bit register. The incrementer has a carry in ( $C_n$ ) input and a carry out ( $C_{n+4}$ ) output to facilitate cascading. The carry in input controls the microprogram counter. When carry in is HIGH the incrementer counts sequentially. The counter register is loaded with the current Y output plus one (Y + 1 \$\phi  $\mu$ PC) on the next clock cycle. When carry in is LOW the incrementer does not count. The microprogram counter register is loaded with the same Y output (Y \$\phi  $\mu$ PC) on the next clock cycle.

#### Stack

The Stack consists of a 4 x 4 memory array and a built-in stack pointer (SP), which always points to the last word written. The stack is used to store return addresses when executing microsubroutines.

The stack pointer is an up/down counter controlled by file enable (FE) and Push/Pop (PUP) inputs. The file enable input allows stack operations only when it is LOW. The Push/Pop input controls the stack pointer position.

The PUSH operation is initiated at the beginning of a microsubroutine. Push/Pop is set HIGH while file enable is kept LOW. The stack pointer is incremented and the memory array is written with the micro-instruction address following the subroutine jump that initiated the push.

The POP operation is initiated at the end of a microsubroutine to obtain the return address. Both Push/Pop and file enable are set LOW. The return address is already available to the multiplexer. The stack pointer is decremented on the next LOW-to-HIGH clock transition, effectively removing old information from the top of the stack. The stack is configured so that data will roll-over if more than four POPs are performed, thus preventing data from being lost.

The contents of the memory position pointed to by the stack pointer is always available to the multiplexer. Stack reference operations can thus be performed without a push or a pop. Since the stack is four words deep, up to four microsubroutines can be nested.

The ZERO input resets the four Y outputs to a binary zero state. The OR inputs (7C909 only) are connected to the Y outputs such that any output can be set to a logical one.

The output enable (OE) input controls the Y outputs. A HIGH on output enable sets the outputs into a high-impedance state.

### **Definition of Terms**

| Name                            | Description                                             |

|---------------------------------|---------------------------------------------------------|

| INPUTS                          |                                                         |

| S <sub>1</sub> , S <sub>0</sub> | Multiplexer Control Lines for Access Source Selection   |

| FE                              | File Enable, Enables Stack Operation, Active LOW        |

| PUP                             | Push/Pop, Selects Stack Operation                       |

| RE                              | Register Enable, Enables Address Register Active LOW    |

| ZERO                            | Forces Output to Logical Zero, Active LOW               |

| ŌĒ                              | Output Enable, Controls Three-State Outputs Active LOW  |

| ORi                             | Logic Or Input to each Address Output Line (7C909 only) |

| Cn                              | Carry In, Controls Microprogram Counter                 |

| R <sub>i</sub>                  | Inputs to the Internal Address Register (7C909 only)    |

| D <sub>i</sub>                  | Direct Inputs to the Multiplexer                        |

| СР                              | Clock Input                                             |

| OUTPUTS                         |                                                         |

| Yi                              | Address Outputs                                         |

| C <sub>n+4</sub>                | Carry Out from Incrementer                              |

## **Definition of Terms** (continued)

| Name            | Description                          |  |

|-----------------|--------------------------------------|--|

| INTERNALSIGNALS |                                      |  |

| μPC             | Contents of the Microprogram Counter |  |

| AR              | Contents of the Address Register     |  |

| STK0 - STK3     | Contents of the Push/Pop Stack       |  |

| SP              | Contents of the Stack Pointer        |  |

| EXTERNALSIGNAL  |                                      |  |

| A               | Address to the Counter Memory        |  |

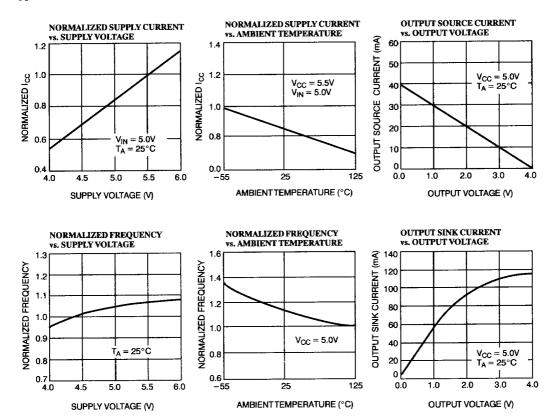

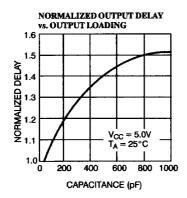

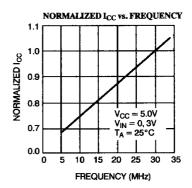

## Typical DC and AC Characteristics

C909-10

## Typical DC and AC Characteristics (continued)

C909-11

## **Ordering Information**

| Clock<br>Cycle<br>(ns) | Ordering Code | Package<br>Type | Operating<br>Range |

|------------------------|---------------|-----------------|--------------------|

| 30                     | CY7C909-30DC  | D16             | Commercial         |

| ,                      | CY7C909-30JC  | J64             | ]                  |

|                        | CY7C909-30PC  | P15             | 1                  |

|                        | CY7C909-30DMB | D16             | Military           |

| 40                     | CY7C909-40DC  | D16             | Commercial         |

|                        | CY7C909-40JC  | J64             |                    |

|                        | CY7C909-40LC  | L64             |                    |

| ŀ                      | CY7C909-40PC  | P15             |                    |

|                        | CY7C909-40DMB | D16             | Military           |

|                        | CY7C909-40LMB | L64             |                    |

| Clock<br>Cycle<br>(ns) | Ordering Code | Package<br>Type | Operating<br>Range |

|------------------------|---------------|-----------------|--------------------|

| 30                     | CY7C911-30DC  | D6              | Commercial         |

|                        | CY7C911-30JC  | J61             |                    |

|                        | CY7C911-30PC  | P5              |                    |

|                        | CY7C911-30DMB | D6              | Military           |

| 40                     | CY7C911-40DC  | D6              | Commercial         |

|                        | CY7C911-40JC  | J61             | 1                  |

|                        | CY7C911-40LC  | L61             | 1                  |

|                        | CY7C911-40PC  | P5              |                    |

|                        | CY7C911-40DMB | D6              | Military           |

|                        | CY7C911-40LMB | L61             | ]                  |

## MILITARY SPECIFICATIONS Group A Subgroup Testing

## **DC** Characteristics

| Parameters           | Subgroups |

|----------------------|-----------|

| V <sub>OH</sub>      | 1, 2, 3   |

| V <sub>OL</sub>      | 1, 2, 3   |

| V <sub>IH</sub>      | 1, 2, 3   |

| V <sub>IL</sub> Max. | 1, 2, 3   |

| $I_{IX}$             | 1, 2, 3   |

| I <sub>OZ</sub>      | 1, 2, 3   |

| I <sub>OS</sub>      | 1, 2, 3   |

| $I_{CC}$             | 1, 2, 3   |

| I <sub>CC1</sub>     | 1, 2, 3   |

**Switching Characteristics**

| Parameters                                  | Subgroups       |

|---------------------------------------------|-----------------|

| Minimum Clock LOW Time                      | 7, 8, 9, 10, 11 |

| Minimum Clock HIGH Time                     | 7, 8, 9, 10, 11 |

| MAXIMUM COMBINATORIAL PRO                   | PAGATION DELAYS |

| D <sub>i</sub> to Y                         | 7, 8, 9, 10, 11 |

| $D_i$ to $C_{n+4}$                          | 7, 8, 9, 10, 11 |

| S <sub>0</sub> , S <sub>1</sub> to Y        | 7, 8, 9, 10, 11 |

| $S_0, S_1 \text{ to } C_{n+4}$              | 7, 8, 9, 10, 11 |

| OR <sub>i</sub> (7C909) to Y                | 7, 8, 9, 10, 11 |

| $OR_i$ (7C909) to $C_{n+4}$                 | 7, 8, 9, 10, 11 |

| $C_n$ to $C_{n+4}$                          | 7, 8, 9, 10, 11 |

| ZERO to C <sub>n+4</sub>                    | 7, 8, 9, 10, 11 |

| Clock HIGH, $S_0$ , $S_1 = LH$ to Y         | 7, 8, 9, 10, 11 |

| Clock HIGH, $S_0$ , $S_1 = LH$ to $C_{n+4}$ | 7, 8, 9, 10, 11 |

| Clock HIGH, $S_0$ , $S_1 = LL$ to Y         | 7, 8, 9, 10, 11 |

| Clock HIGH, $S_0$ , $S_1 = LL$ to $C_{n+4}$ | 7, 8, 9, 10, 11 |

| Clock HIGH, $S_0$ , $S_1 = HL$ to Y         | 7, 8, 9, 10, 11 |

| Clock HIGH, $S_0$ , $S_1 = HL$ to $C_{n+4}$ | 7, 8, 9, 10, 11 |

| Parameters                                  | Subgroups       |  |  |  |

|---------------------------------------------|-----------------|--|--|--|

| MINIMUM SET-UP AND HOLD TIMES               |                 |  |  |  |

| RE Set-Up Time                              | 7, 8, 9, 10, 11 |  |  |  |

| RE Hold Time                                | 7, 8, 9, 10, 11 |  |  |  |

| Push/Pop Set-Up Time                        | 7, 8, 9, 10, 11 |  |  |  |

| Push/Pop Hold Time                          | 7, 8, 9, 10, 11 |  |  |  |

| FE Set-Up Time                              | 7, 8, 9, 10, 11 |  |  |  |

| FE Hold Time                                | 7, 8, 9, 10, 11 |  |  |  |

| C <sub>n</sub> Set-Up Time                  | 7, 8, 9, 10, 11 |  |  |  |

| C <sub>n</sub> Hold Time                    | 7, 8, 9, 10, 11 |  |  |  |

| D <sub>i</sub> Set-Up Time                  | 7, 8, 9, 10, 11 |  |  |  |

| D <sub>i</sub> Hold Time                    | 7, 8, 9, 10, 11 |  |  |  |

| OR <sub>i</sub> (7C909) Set-Up Time         | 7, 8, 9, 10, 11 |  |  |  |

| OR <sub>i</sub> (7C909) Hold Time           | 7, 8, 9, 10, 11 |  |  |  |

| S <sub>0</sub> , S <sub>1</sub> Set-Up Time | 7, 8, 9, 10, 11 |  |  |  |

| S <sub>0</sub> , S <sub>1</sub> Hold Time   | 7, 8, 9, 10, 11 |  |  |  |

| ZERO Set-Up Time                            | 7, 8, 9, 10, 11 |  |  |  |

| ZERO Hold Time                              | 7, 8, 9, 10, 11 |  |  |  |

Document #: 38-00015-B