#### Features

- Fast

- CY7C901 23 has a 23-ns read-modify-write cycle; Commercial 25% faster than "C" Spec 2901

- CY7C901-27 has a 27-ns read-modify-write cycle; Military 15% faster than "C" Spec 2901

- Low power

- 70 mA (commercial)

- 90 mA (military)

- V<sub>CC</sub> of 5V ±10% (commercial and military)

- Eight-function ALU

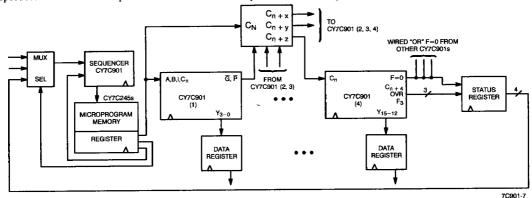

- Infinitely expandable in 4-bit increments

- Four status flags: carry, overflow, negative, zero

- Capable of withstanding greater than 2000V static discharge voltage

- Pin compatible and functional equivalent to Am2901B, C

#### **Functional Description**

The CY7C901 is a high-speed, expandable, 4-bit wide ALU that can be used to implement the arithmetic section of a CPU, peripheral controller, or programmable controller. The instruction set of the CY7C901 is basic but yet so versatile that it can emulate the ALU of almost any digital computer.

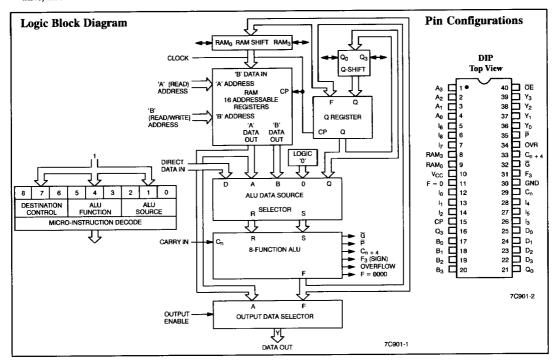

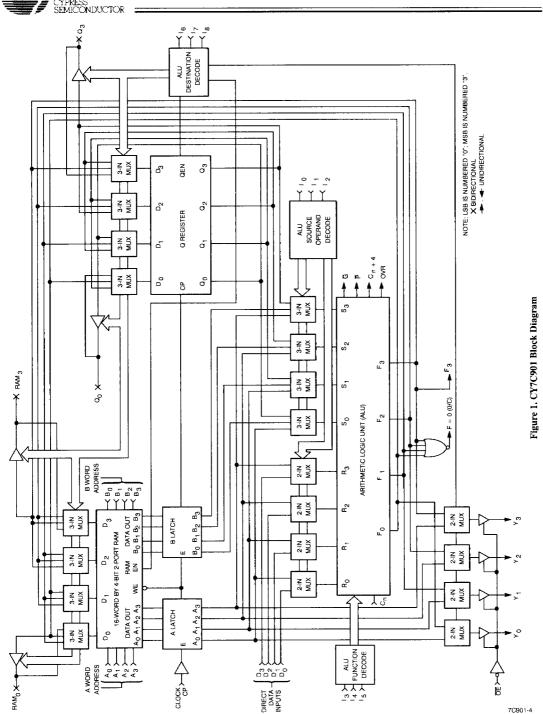

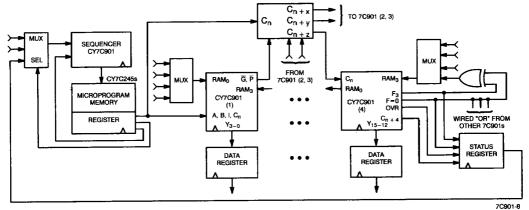

The CY7C901, as illustrated in the block diagram, consists of a 16-word by 4-bit dual-port RAM register file, a 4-bit ALU, and the required data manipulation and controllogic.

# CMOS Four-Bit Slice

The operation performed is determined by nine input control lines (I<sub>0</sub> to I<sub>8</sub>) that are usually inputs from a micro-instruction register.

The CY7C901 is expandable in 4-bit increments, has three-state data outputs as well as flag outputs, and can use either a full look-aheadcarry or a ripple carry.

The CY7C901 is a pin-compatible, functionally equivalent, improved-performance replacement for the Am2901.

The CY7C901 is fabricated using an advanced 1.2-micron CMOS process that eliminateslatch-up, provides ESD protection over 2000V, and achieves superior performanceat low-power dissipation.

## **Selection Guide**

| Minimum Read-Modify-Write Cycle (ns) | Maximum Operating I <sub>CC</sub> (mA) | Operating Range | Part Number |

|--------------------------------------|----------------------------------------|-----------------|-------------|

| 23                                   | 80                                     | Commercial      | CY7C901-23  |

| 27                                   | 90                                     | Military        | CY7C901-27  |

| 31                                   | 70                                     | Commercial      | CY7C901-31  |

| 32                                   | 90                                     | Military        | CY7C901-32  |

Pin Definitions

## Pin Configurations (continued)

#

LCC

## **Maximum Ratings**

(Above which the useful life may be impaired. For user guidelines, not tested.)

| Storage Temperature $\ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \$              |

|--------------------------------------------------------------------------|

| $\begin{tabular}{lllllllllllllllllllllllllllllllllll$                    |

| Supply Voltage to Ground Potential (Pin 11 to Pin 33) $-0.5V$ to $+7.0V$ |

| DC Voltage Applied to Outputs in High Z State $-0.5V$ to $+7.0V$         |

| DC Input Voltage 3.0V to +7.0V                                           |

| Output Current into Outputs (LOW)                                        |

| Static Discharge Voltage                                                 |

| Latch-Up Current (Outputs) >200 mA                                       |

# **Operating Range**

| Range                   | Ambient<br>Temperature | v <sub>cc</sub> |

|-------------------------|------------------------|-----------------|

| Commercial              | 0°C to +70°C           | 5V ±10%         |

| Military <sup>[1]</sup> | - 55°C to +125°C       | 5V ±10%         |

## Notes:

1. TA is the "instant on" case temperature.

| Signal<br>Name | I/O | Description                                                                                                                                                                                                           |

|----------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $A_0 - A_3$    | I   | These four address lines select one of the registers in the stack and output its contents on the (internal) A port.                                                                                                   |

| $B_0 - B_3$    | I   | These four address lines select one of the registers in the stack and output its contents on the (internal) B port. This can also be the destination address when data is written back into the register file.        |

| $I_0 - I_8$    | I   | These nine instruction lines select the ALU data sources $(I_0, 1, 2)$ , the operation to be performed $(I_3, 4, 5)$ , and what data is to be written into either the Q register or the register file $(I_6, 7, 8)$ . |

| $D_0 - D_3$    | I   | These are four data input lines that may be selected by the $I_{0,\ 1,\ 2}$ lines as inputs to the ALU.                                                                                                               |

| $Y_0 - Y_3$    | О   | These are three-state data output lines that, when enabled, output either the output of the ALU or the data in the A latches, as determined by the code on the $I_{6,7,8}$ lines.                                     |

| ŌĒ             | Ι   | Output Enable. This is an active LOW input that controls the $Y_0-Y_3$ outputs. When this signal is LOW the Y outputs are enabled and when it is HIGH they are in the high-impedance.                                 |

dance state.

| Signal<br>Name                     | I/O | Description                                                                                                                                                                                                                                                                                                                                |

|------------------------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CP                                 | I   | Clock Input. The LOW level of the clock writes data to the 16 x 4 RAM. The HIGH level of the clock writes data from the RAM to the A-port and B-port latches. The operation of the Q register is similar. Data is entered into the master latch on the LOW level of the clock and transferred from master to slave when the clock is HIGH. |

| Q <sub>3</sub><br>RAM <sub>3</sub> | I/O | These two lines are bidirectional and are controlled by the I <sub>6,7,8</sub> inputs. Electrically they are three-state output drivers connected to the TTL-compatible CMOS inputs.                                                                                                                                                       |

|                                    |     | Outputs: When the destination code on lines $I_6$ , $7$ , $8$ indicates a shift left (UP) operation the three-state outputs are enabled and the MSB of the Q register is output on the $Q_3$ pin and the MSB of the ALU output $(F_3)$ is output on the RAM <sub>3</sub> pin.                                                              |

|                                    |     | Inputs: When the destination code indicates a shift right (DOWN) the pins are the data inputs to the MSB of the Q register and the MSB of the RAM.                                                                                                                                                                                         |

| Q <sub>0</sub><br>RAM <sub>0</sub> | I/O | These two lines are bidirectional and function in a manner similar to the $Q_3$ and $RAM_3$ lines, except that they are the LSB of the Q register and RAM.                                                                                                                                                                                 |

| $C_n$                              | I   | The carry-in to the internal ALU.                                                                                                                                                                                                                                                                                                          |

| $C_{n+4}$                          | O   | The carry-out from the internal ALU.                                                                                                                                                                                                                                                                                                       |

#### Pin Definitions (continued)

| Signal<br>Name | I/O | Description                                                                                                                                                                                                                                                                                                                        |

|----------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| G, P           | 0   | The carry generate and the carry propagate outputs of the ALU, which may be used to perform a carry look-ahead operation over the 4 bits of the ALU.                                                                                                                                                                               |

| OVR            | 0   | Overflow. This signal is logically the exclusive-<br>OR of the carry-in and the carry-out of the<br>MSB of the ALU. This pin indicates that the<br>result of the ALU operation has exceeded the<br>capacity of the machine. It is valid only when<br>the sign bits of the operands are identical (add)<br>or opposite (substract). |

| F = 0          | 0   | Open collector output that goes HIGH if the data on the ALU outputs $(F_{0,1,2,3})$ are all LOW. It indicates that the result of an ALU operation is zero.                                                                                                                                                                         |

| F <sub>3</sub> | О   | The most significant bit of the ALU output.                                                                                                                                                                                                                                                                                        |

#### **Description of Architecture**

#### **General Description**

A block diagram of the CY7C901 is shown in Figure 1. The circuit is a 4-bit slice consisting of a register file (16 x 4 dual-port RAM), the ALU, the Q register, and the necessary control logic. It is expandable in 4-bit increments.

#### RAM

The RAM is addressed by two 4-bit address fields  $(A_0-A_3,B_0-B_3)$  that cause the data to appear at the A or B (internal) ports. If the A and B addresses are the same, the data at the A and B ports will be identical.

New data is written into the RAM location specified by the B address when the RAM write enable (RAM EN) is active and clock input is LOW. Each of the four RAM inputs is driven by a 3-input multiplexer that allows the outputs of the ALU ( $F_0$ , 1, 2, 3) to be shifted one bit position to the left, the right, or not to be shifted. The other inputs to the multiplexer are from the RAM3 and RAM0 I/O pins.

For a shift left (up) operation, the RAM<sub>3</sub> output buffer is enabled and the RAM<sub>0</sub> multiplexer input is enabled. For a shift right (down) operation the RAM<sub>0</sub> output buffer is enabled and the RAM<sub>3</sub> multiplexer input is enabled.

The data to be written into the RAM is applied to the D inputs of the CY7C901 and is passed (unchanged) through the ALU to the RAM location addressed by the B word address.

The outputs of the RAM A and B ports drive separate 4-bit latches that are enabled (follow the RAM data) when the clock is HIGH. The outputs of the A latches go to three multiplexers whose outputs drive the two inputs to the ALU  $(R_0, 1, 2, 3)$  and  $(S_0, 1, 2, 3)$  and the  $(Y_0, 1, 2, 3)$  chip outputs.

#### ALU (Arithmetic Logic Unit)

The ALU can perform three arithmetic and five logical operations on two 4-bit input words, R and S. The R inputs are driven from four 2-input multiplexers whose inputs are from either the (RAM) A-port or the external data (D) inputs. The S inputs are driven from four 3-input multiplexers whose inputs are from the A-port, the B-port, or the Q register. Both multiplexers are controlled by the  $I_0,\ 1,\ 2$  inputs as shown in  $Table\ I$ . This configuration of multiplexers on the ALU R and S inputs enables the user to select eight pairs of combinations of A, B, D, Q, and "0" (unselected) inputs as 4-bit operands to the ALU. The logical and arithmetic operations performed by the ALU upon the data present at its R and S inputs are tabulated in  $Table\ 2$ . The ALU has a carry-in  $(C_0)$  input, carry-propagate (P) output, carry-generate (G) output, carry-out  $(C_{n+4})$  and overflow (OVR) pins to enable the user to (1) speed up arithmetic operations by implementing carry look-ahead logic and (2) determine if an arithmetic overflow has occurred.

As shown in Table 3, the ALU data outputs  $(F_{0,\,1,\,2,\,3})$  are routed to the RAM, the Q register inputs, and the Y outputs under control of the  $I_{6,\,7,\,8}$  control signal inputs. In addition, the MSB of the ALU is output as F3 so that the user can examine the sign bit without enabling the three-state outputs. The F=0 output, used for zero detection is HIGH when all bits of the F output are LOW. It is an open-drain output which may be wire ORed across multiple 7C901 processor slices.

#### O Register

The Q register functions as an accumulator or temporary storage register. Physically it is a 4-bit register implemented with master-slave latches. The inputs to the Q register are driven by the outputs from four 3-input multiplexers under control of the  $I_{6,7,8}$  inputs. The  $Q_0$  and  $Q_3$  I/O pins function in a manner similar to the RAM0 and RAM3 pins. The other inputs to the multiplexer enable the contents of the Q register to be shifted up or down, or the outputs of the ALU to be entered into the master latches. Data is entered into the master latches when the clock is LOW and transferred from master to slave (output) when the clock changes from LOW to HIGH.

#### ALU Source Operand and ALU Functions

The ALU source operands and ALU function matrix is summarized in *Table 4* and separated by logic operation or arithmetic operation in *Tables 5* and  $\delta$ , respectively. The  $I_{0,1,2}$  lines select eight pairs of source operands and the  $I_{3,4,5}$  lines select the operation to be performed. The carry-in  $(C_n)$  signal affects the arithmetic result and the internal flags; not the logical operations.

#### Conventional Addition and Pass-Increment/Decrement

When the carry-in is HIGH and either a conventional addition or a pass operation is performed, one (1) is added to the result. If the decrement operation is performed when the carry-in is LOW, the value of the operand is reduced by one. However, when the same operation is performed when the carry-in is HIGH, it nullifies the decrement operations ot that the result is equivalent to the pass operation.

#### Subtraction

Recall that in two's complement integer coding -1 is equal to all ones, and that in one's complement integer coding zero is equal to all ones. To convert a positive integer to its two's complement (negative) equivalent, invert (complement) the number and add 1 to it; i.e., TWC = ONC + 1. In *Table 6* the symbol -Q represents the two's complement of Q so that the one's complement of Q is then -Q - 1.

7C901-4

#### **Functional Tables**

**Table 1. ALU Source Operand Control**

|          |                | Mic            | ro Coc         | le            | ALU Source<br>Operands |   |  |

|----------|----------------|----------------|----------------|---------------|------------------------|---|--|

| Mnemonic | I <sub>2</sub> | I <sub>1</sub> | I <sub>0</sub> | Octal<br>Code | R                      | S |  |

| AQ       | L              | L              | L              | 0             | A                      | Q |  |

| AB       | L              | L '            | Н              | 1             | Α                      | В |  |

| ZQ       | L              | Н              | L              | 2             | 0                      | Q |  |

| ZB       | L              | Н              | Н              | 3             | 0                      | В |  |

| ZA       | H              | L              | L              | 4             | 0                      | A |  |

| DA       | Н              | L              | H              | 5             | D                      | A |  |

| DQ       | Н              | Н              | L              | 6             | D                      | Q |  |

| DZ       | Н              | Н              | Н              | 7             | D                      | 0 |  |

**Table 2. ALU Function Control**

|          |   | Mic | ro Co         | ode             |                      |                                           |

|----------|---|-----|---------------|-----------------|----------------------|-------------------------------------------|

| Mnemonic |   |     | Octal<br>Code | ALU<br>Function | Symbol               |                                           |

| ADD      | L | L   | L             | 0               | R Plus S             | R + S                                     |

| SUBR     | L | L   | Н             | 1               | S Minus R            | S – R                                     |

| SUBS     | L | Н   | L             | 2               | R Minus S            | R – S                                     |

| OR       | L | Н   | Н             | 3               | RORS                 | R∨S                                       |

| AND      | Н | L   | L             | 4               | R AND S              | R∧S                                       |

| NOTRS    | Н | L   | Н             | 5               | $\overline{R}$ AND S | $\overline{\mathbf{R}} \wedge \mathbf{S}$ |

| XOR      | Н | Н   | L             | 6               | R XOR S              | R¥S                                       |

| XNOR     | Н | Н   | Н             | 7               | R XNOR S             | $\overline{R \vee S}$                     |

**Table 3. ALU Destination Control**

|          |                | Mic            | ro Co          | łe            | RAM F | unction        | Q-Reg. | Function |             | RAM Shifte       |                  | Q Shifter      |                 |

|----------|----------------|----------------|----------------|---------------|-------|----------------|--------|----------|-------------|------------------|------------------|----------------|-----------------|

| Mnemonic | I <sub>8</sub> | I <sub>7</sub> | I <sub>6</sub> | Octal<br>Code | Shift | Load           | Shift  | Load     | Y<br>Output | RAM <sub>0</sub> | RAM <sub>3</sub> | Q <sub>0</sub> | Q <sub>3</sub>  |

| QREG     | L              | L              | L              | 0             | X     | None           | None   | F∳Q      | F           | X                | X                | X              | X               |

| NOP      | L              | L              | Н              | 1             | X     | None           | X      | None     | F           | X                | X                | X              | X               |

| RAMA     | L              | Н              | L              | 2             | None  | F♦B            | Х      | None     | A           | X                | X                | X              | X               |

| RAMF     | L              | Н              | Н              | 3             | None  | F♦B            | X      | None     | F           | X                | X                | X              | X               |

| RAMQD    | Н              | L              | L              | 4             | DOWN  | F/2 <b>♦</b> B | DOWN   | Q/2 ♦ Q  | F           | $F_0$            | IN <sub>3</sub>  | $Q_0$          | IN <sub>3</sub> |

| RAMD     | Н              | L              | Н              | 5             | DOWN  | F/2 <b>♦</b> B | X      | None     | F           | $\mathbf{F}_0$   | IN <sub>3</sub>  | $Q_0$          | X               |

| RAMQU    | Н              | Н              | L              | 6             | UP    | 2F ♦ B         | UP     | 2Q ≱ Q   | F           | IN <sub>0</sub>  | F <sub>3</sub>   | $IN_0$         | Q <sub>3</sub>  |

| RAMU     | Н              | Н              | Н              | 7             | UP    | 2F ♦ B         | Х      | None     | F           | IN <sub>0</sub>  | F <sub>3</sub>   | X              | Q <sub>3</sub>  |

X = Don't care. Electrically, the input shift pin is a TTL input internally connected to a three-state output that is in the high-impedance state.

Table 4. Source Operand and ALU Function Matrix

|                           | I <sub>210</sub> Octal                                | 0                                         | 1                                         | 2              | 3              | 4              | 5                                         | 6                                         | 7              |

|---------------------------|-------------------------------------------------------|-------------------------------------------|-------------------------------------------|----------------|----------------|----------------|-------------------------------------------|-------------------------------------------|----------------|

| Octal<br>I <sub>543</sub> | ALU Source<br>ALU Function                            | A, Q                                      | A, B                                      | 0, Q           | O, B           | O, A           | D, A                                      | D, Q                                      | D, O           |

| 0                         | $C_n = L$ $R$ plus $S$ $C_n = H$                      | A + Q<br>A + Q + 1                        | A + B<br>A + B + 1                        | Q<br>Q+1       | B<br>B+1       | A<br>A + 1     | D + A $D + A + 1$                         | D + Q $D + Q + 1$                         | D<br>D + 1     |

| 1                         | C <sub>n</sub> = L<br>S minus R<br>C <sub>n</sub> = H | Q - A - 1<br>Q - A                        | B – A – 1<br>B – A                        | Q - 1<br>Q     | B – 1<br>B     | A – 1<br>A     | A – D – 1<br>A – D                        | Q - D - 1<br>Q - D                        | - D - 1<br>- D |

| 2                         | C <sub>n</sub> = L<br>R minus S<br>C <sub>n</sub> = H | A - Q - 1 $A - Q$                         | A – B – 1<br>A – B                        | - Q - 1<br>- Q | - B - 1<br>- B | - A - 1<br>- A | D - A - 1<br>D - A                        | D – Q – 1<br>D – Q                        | D – 1<br>D     |

| 3                         | RORS                                                  | ΑVQ                                       | A∨B                                       | Q              | В              | Α              | D∨A                                       | D∨Q                                       | D              |

| 4                         | R AND S                                               | $A \wedge Q$                              | A∧B                                       | 0              | 0              | 0              | D∧A                                       | $\mathbf{D} \wedge \mathbf{Q}$            | 0              |

| 5                         | R AND S                                               | $\overline{\mathbf{A}} \wedge \mathbf{Q}$ | $\overline{\mathbf{A}} \wedge \mathbf{B}$ | Q              | В              | Α              | $\overline{\mathbf{D}} \wedge \mathbf{A}$ | $\overline{\mathbf{D}} \wedge \mathbf{Q}$ | 0              |

| 6                         | RXORS                                                 | A¥Q                                       | A¥B                                       | Q              | В              | A              | D∀A                                       | D∀Q                                       | D              |

| 7                         | R XNOR S                                              | $\overline{A \lor Q}$                     | $\overline{A \vee B}$                     | Q              | B              | Ā              | D∀A                                       | $\overline{D \lor Q}$                     | D              |

$<sup>+ =</sup> Plus; - = Minus; \lor = OR; \land = AND; \lor = XOR$

A = Register addressed by A inputs. B = Register addressed by B inputs.

UP is toward MSB, DOWN is toward LSB.

**Table 5. ALU Logic Mode Functions**

| Octal<br>I <sub>543</sub> , I <sub>210</sub> | Group  | Function                                  |

|----------------------------------------------|--------|-------------------------------------------|

| 40                                           | AND    | $A \wedge Q$                              |

| 4 1                                          |        | $\mathbf{A} \wedge \mathbf{B}$            |

| 4 5                                          |        | $\mathbf{D} \wedge \mathbf{A}$            |

| 46                                           |        | $\mathbf{D} \wedge \mathbf{Q}$            |

| 3 0                                          | OR     | $A \lor Q$                                |

| 3 1                                          |        | $A \lor B$                                |

| 3 5                                          |        | D∨A                                       |

| 3 6                                          |        | $\mathbf{D} \lor \mathbf{Q}$              |

| 60                                           | XOR    | A∀Q                                       |

| 6 1                                          |        | $A \forall B$                             |

| 6 5                                          |        | D∀A                                       |

| 66                                           |        | D∀Q                                       |

| 7 0                                          | XNOR   | $\overline{A \vee Q}$                     |

| 7 1                                          |        | $\overline{A \lor B}$                     |

| 7 5                                          |        | $\overline{\mathbf{D} \vee \mathbf{A}}$   |

| 76                                           |        | $\overline{\mathbf{D} \vee \mathbf{Q}}$   |

| 72                                           | INVERT | Q                                         |

| 7 3                                          |        | B                                         |

| 7 4                                          |        | Ā                                         |

| 77                                           |        | $\overline{\mathbf{D}}$                   |

| 62                                           | PASS   | Q                                         |

| 63                                           |        | В                                         |

| 64                                           |        | Α                                         |

| 67                                           |        | D                                         |

| 32                                           | PASS   | Q                                         |

| 33                                           |        | В                                         |

| 3 4                                          |        | A                                         |

| 3 7                                          |        | D                                         |

| 42                                           | "ZERO" | 0                                         |

| 4 3                                          |        | 0                                         |

| 4 4                                          |        | 0                                         |

| 47                                           |        | 0                                         |

| 50                                           | MASK   | $\overline{\mathbf{A}} \wedge \mathbf{Q}$ |

| 51                                           |        | $\overline{\mathbf{A}} \wedge \mathbf{B}$ |

| 5 5                                          |        | $\overline{\mathbf{D}} \wedge \mathbf{A}$ |

| 56                                           |        | $\overline{\mathbf{D}} \wedge \mathbf{Q}$ |

**Table 6. ALU Arithmetic Mode Functions**

| Octal<br>I <sub>543</sub> , | $C_n = 0$   | (LOW)     | $C_n = 1$   | (HIGH)    |

|-----------------------------|-------------|-----------|-------------|-----------|

| I <sub>210</sub>            | Group       | Function  | Group       | Function  |

| 0.0                         | ADD         | A+Q       | ADD plus    | A+Q+1     |

| 01                          |             | A + B     | one         | A + B + 1 |

| 0.5                         |             | D + A     |             | D+A+1     |

| 06                          |             | D + Q     |             | D+Q+1     |

| 02                          | PASS        | Q         | Increment   | Q + 1     |

| 03                          |             | В         |             | B + 1     |

| 04                          |             | A         |             | A + 1     |

| 07                          |             | D         |             | D + 1     |

| 12                          | Decrement   | Q – 1     | PASS        | Q         |

| 13                          |             | B - 1     |             | В         |

| 14                          |             | A – 1     |             | Α         |

| 27                          |             | D – 1     |             | D         |

| 22                          | 1's Comp.   | - Q - 1   | 2's Comp.   | - Q       |

| 23                          |             | - B - 1   | (Negate)    | – B       |

| 24                          |             | - A - 1   |             | – A       |

| 17                          |             | - D - 1   |             | – D       |

| 10                          | Subtract    | Q – A – 1 | Subtract    | Q – A     |

| 11                          | (1's Comp.) | B – A – 1 | (2's Comp.) | B – A     |

| 15                          |             | A – D – 1 |             | A – D     |

| 16                          |             | Q-D-1     |             | Q – D     |

| 20                          |             | A – Q – 1 |             | A – Q     |

| 21                          |             | A – B – 1 |             | A – B     |

| 2.5                         |             | D - A - 1 |             | D – A     |

| 26                          |             | D-Q-1     |             | D – Q     |

# Logic Functions for $\overline{G}$ , $\overline{P}$ , $C_{n+4}$ , and OVR

The four signals  $\overline{G}$ ,  $\overline{P}$ ,  $C_{n+4}$ , and OVR are designed to indicate carry and overflow conditions when the CY7C901 is in the add or subtract mode. Table 7 indicates the logic equations for these four signals for each of the eight ALU functions. The R and S inputs are the two inputs selected according to Table 1.

#### Definitions (+ = OR)

| $P_0 = R_0 + S_0$                            | $G_0 = R_0 S_0$                                           |

|----------------------------------------------|-----------------------------------------------------------|

| $\mathbf{P}_1 = \mathbf{R}_1 + \mathbf{S}_1$ | $G_1 = R_1 S_1$                                           |

| $\mathbf{P}_2 = \mathbf{R}_2 + \mathbf{S}_2$ | $G_2 = R_2 S_2$                                           |

| $P_3 = R_3 + S_3$                            | $G_3 = R_3S_3$                                            |

| $C_4 = G_3 + P_3G_2 + P_3P_3$                | $_{2}G_{1} + P_{3}P_{2}G_{0} + P_{3}P_{2}P_{1}P_{0}C_{n}$ |

| $C_2 = G_2 + P_2G_1 + P_2P_1$                | Go + PaPaPoCa                                             |

## Table 7. $\overline{G}$ , $\overline{P}$ , $C_{n+p}$ and OVR Logic Functions

| I <sub>543</sub> | Function                                  | P                         | Ğ                                                    | C <sub>n + 4</sub>                                                                 | OVR                             |

|------------------|-------------------------------------------|---------------------------|------------------------------------------------------|------------------------------------------------------------------------------------|---------------------------------|

| 0                | R+S                                       | $\overline{P_3P_2P_1P_0}$ | $\overline{G_3 + P_3G_2 + P_3P_2G_1 + P_3P_2P_1G_0}$ | C <sub>4</sub>                                                                     | C <sub>3</sub> ¥ C <sub>4</sub> |

| 1                | S-R                                       | •                         | Same as R + S equations, but su                      | ubstitute Ri for Ri in definition                                                  | ons •                           |

| 2                | R-S                                       | •                         | Same as R + S equations, but s                       | ubstitute Si for Si in definitio                                                   | ns •                            |

| 3                | $R \vee S$                                | LOW                       | $P_3P_2P_1P_0$                                       | $\overline{P_3P_2P_1P_0} + C_n$                                                    | $\overline{P_3P_2P_1P_0} + C_n$ |

| 4                | RAS                                       | LOW                       | $G_3 + G_2 + G_1 + G_0$                              | $G_3+G_2+G_1+G_0+C_n$                                                              | $G_3+G_2+G_1+G_0+C_n$           |

| 5                | $\overline{\mathbb{R}} \wedge \mathbb{S}$ | LOW                       | Same as R ∧ S equa                                   | tions, but substitute Ri for R                                                     | in definitions •                |

| 6                | R¥S                                       |                           | $lack$ Same as $\overline{R \vee S}$                 | , but substitute $\overline{R_i}$ for $R_i$ in de                                  | efinitions                      |

| 7                | R¥S                                       | $G_3 + G_2 + G_1 + G_0$   | $G_3 + P_3G_2 + P_3P_2G_1 + P_3P_2P_1G_0$            | $\frac{\overline{G_3 + P_3G_2 + P_3P_2G_1}}{+ P_3P_2P_1P_0(G_0 + \overline{C_n})}$ | Note 2                          |

#### Notes:

$<sup>\</sup>begin{array}{ll} 2. & [P_2+G_2P_1+\overline{G}_2\overline{G}_1\overline{P}_0+\overline{G}_2\overline{G}_1\overline{G}_0C_n] \vee [\overline{P}_3+\overline{G}_3\overline{P}_2+\overline{G}_3\overline{G}_2\overline{P}_1+\overline{G}_3\overline{G}_2\overline{G}_1\overline{P}_0+\overline{G}_3\overline{G}_2\overline{G}_1\overline{G}_0C_n] \\ & +=OR \end{array}$

# Electrical Characteristics Over Commercial and Military Operating Range [3, 4]

| Parameters       | Description                                 | Test Condition                                                     | ons               | Min.     | Max. | Units |

|------------------|---------------------------------------------|--------------------------------------------------------------------|-------------------|----------|------|-------|

| V <sub>OH</sub>  | Output HIGH Voltage                         | $V_{CC} = Min., I_{OH} = -3.4 \text{ mA}$                          |                   | 2.4      |      | V     |

| $V_{OL}$         | Output LOW Voltage                          | $V_{CC} = Min.,$ $I_{OL} = 20 \text{ mA Commercial}, 16 \text{ m}$ | nA Military       |          | 0.4  | V     |

| V <sub>IH</sub>  | Input HIGH Voltage                          |                                                                    | 2.0               | $V_{CC}$ | V    |       |

| V <sub>IL</sub>  | Input LOW Voltage                           |                                                                    | - 3.0             | 0.8      | v    |       |

| I <sub>IX</sub>  | Input LeakageCurrent                        | $V_{SS} \le V_{IN} \le V_{CC}$ , $V_{CC} = Max$                    | - 10              | 10       | μА   |       |

| I <sub>OH</sub>  | Output HIGH Current                         | $V_{\rm CC}$ = Min., $V_{\rm OH}$ = 2.4V                           | - 3.4             | T        | mA   |       |

| I <sub>OL</sub>  | Output LOW Current                          | $V_{\rm CC} = Min., V_{\rm OL} = 0.4V$                             | Commercial        | 20       |      | mA    |

|                  |                                             |                                                                    | Military          | 16       |      | 1     |

| I <sub>OZ</sub>  | Output LeakageCurrent                       | $V_{CC} = Max., V_{OUT} = V_{SS}$ to $V_{CC}$                      | cc ·              | -40      | +40  | μA    |

| $I_{SC}$         | Output Short Circuit Current <sup>[5]</sup> | $V_{CC} = Max., V_{OUT} = 0V$                                      |                   |          | - 85 | mA    |

| $I_{CC}$         | Supply Current                              | V <sub>CC</sub> = Max.                                             | Commercial -31    |          | 70   | mA    |

|                  |                                             |                                                                    | Commercial -23    |          | 80   | 1     |

|                  |                                             |                                                                    | Military -27, -32 |          | 90   | 1     |

| I <sub>CC1</sub> | Supply Current                              | $V_{IH} \ge V_{CC} - 1.2V$ , 10 MHz,                               | Commercial        |          | 26.5 | mA    |

|                  |                                             | $V_{IL} \leq 0.4V$                                                 | Military          |          | 31   | 1     |

#### Capacitance<sup>[6]</sup>

| Parameters      | Description        | Test Conditions                         | Max. | Units |

|-----------------|--------------------|-----------------------------------------|------|-------|

| C <sub>IN</sub> | InputCapacitance   | $T_A = 25^{\circ}C, f = 1 \text{ MHz},$ | 5    | pF    |

| $C_{OUT}$       | Output Capacitance | $V_{\rm CC} = 5.0 V$                    | 7    | pF    |

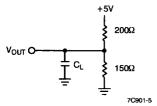

# Output Loads used for AC Performance Characteristics<sup>[7, 8, 9]</sup>

#### All outputs except open drain

Open drain (F = 0)

#### Notes:

- See the last page of this specification for Group A subgroup testing information.

- 4.  $V_{CC}$  Min. = 4.5V,  $V_{CC}$  Max. = 5.5V

- Not more than one output should be shorted at a time. Duration of the short circuit should not be more than one second.

- Tested initially and after any design or process changes that may affect these parameters.

- . C<sub>L</sub> = 50 pF includes scope probe, wiring and stray capacitance.

- 8.  $C_L = 5 pF$  for output disable tests.

- Loads shown above are for commercial (20 mA) I<sub>OL</sub> specifications only.

# CY7C901-23 Commercial and CY7C901-27 Military AC Performance Characteristics

The tables below specify the guaranteed AC performance of these devices over the commercial (0°C to 70°C) and military ( $-55^{\circ}$ C to  $+125^{\circ}$ C) operating temperature range with  $V_{\rm CC}$  varying from 4.5V to 5.5V. All times are in nanoseconds and are measured between the 1.5V signal levels. The inputs switch between 0V and 3V with signal transition rates of 1V per nanosecond. All outputs have maximum DC current loads. See "Electrical Characteristics" for loading circuit information.

This data applies to parts with the following numbers:

CY7C901 – 23PC CY7C901 – 23DC CY7C901 – 23LC CY7C901 – 27LMB CY7C901 – 27LMB

# Cycle Time and Clock Characteristics<sup>[2]</sup>

| CY7C901                                                                    | -23    | -27    |

|----------------------------------------------------------------------------|--------|--------|

| Read-Modify-Write Cycle (from selection of A, B registers to end of cycle) | 23 ns  | 27 ns  |

| Maximum Clock Frequency to shift Q (50% duty cycle, I = 432 or 632)        | 43 MHz | 37 MHz |

| Minimum Clock LOW Time                                                     | 13 ns  | 15 ns  |

| Minimum Clock HIGH Time                                                    | 10 ns  | 12 ns  |

| Minimum Clock Period                                                       | 23 ns  | 27 ns  |

# Combinatorial Propagation Delays (C<sub>I.</sub> = 50 pF)[3, 10]

| To Output              | 7  | 7  | F        | 3  | C,       | +4       | Ğ, | P  | F: | = 0 | 70 | /R | RA | Mę | Q  | 20 |

|------------------------|----|----|----------|----|----------|----------|----|----|----|-----|----|----|----|----|----|----|

| From Input             | 7  | 7  | F        | 3  | C.       | +4       | G, | P  | F= | = 0 | 70 | /R | RA | М3 | Ç  | 23 |

| Speed (ns)             | 23 | 27 | 23       | 27 | 23       | 27       | 23 | 27 | 23 | 27  | 23 | 27 | 23 | 27 | 23 | 27 |

| A, B Address           | 30 | 33 | 30       | 33 | 30       | 33       | 28 | 33 | 30 | 33  | 30 | 33 | 30 | 33 |    | _  |

| D                      | 21 | 24 | 20       | 23 | 20       | 23       | 20 | 21 | 24 | 25  | 21 | 24 | 22 | 25 | _  | _  |

| Cn                     | 17 | 18 | 16       | 17 | 14       | 14       | _  | _  | 18 | 19  | 16 | 17 | 18 | 19 | _  | _  |

| I <sub>0,1,2</sub>     | 26 | 28 | 25       | 27 | 24       | 26       | 24 | 28 | 25 | 29  | 24 | 27 | 25 | 27 | _  |    |

| I <sub>3,4,5</sub>     | 26 | 27 | 24       | 27 | 24       | 26       | 24 | 26 | 26 | 27  | 24 | 26 | 26 | 27 | _  | _  |

| I <sub>6,7,8</sub>     | 16 | 18 | <u> </u> | _  | =        | <b>—</b> | _  | _  | _  | _   | _  | _  | 21 | 21 | 21 | 21 |

| A Bypass ALU (I = 2XX) | 24 | 26 | <u> </u> | -  | <u> </u> |          | _  |    | _  |     | _  | -  | _  |    |    |    |

| Clock (LOW to HIGH)    | 24 | 27 | 23       | 26 | 23       | 26       | 23 | 25 | 24 | 27  | 24 | 26 | 24 | 27 | 19 | 20 |

# Set-Up and Hold Times Relative to Clock (CP) Input[3, 10, 11]

|                                         | СР: —                        | 7            |          |                   |                          |                              |    | _  |  |    |  |      |  |   |

|-----------------------------------------|------------------------------|--------------|----------|-------------------|--------------------------|------------------------------|----|----|--|----|--|------|--|---|

|                                         | Set-U <sub>l</sub><br>Before | pTime<br>H∳L |          | I Time<br>r H ♦ L | Set-Uj<br>Before         | Set-Up Time<br>Before L \$ H |    |    |  |    |  |      |  |   |

| Speed (ns)                              | 23                           | 27           | 23       | 27                | 23                       | 27                           | 23 | 27 |  |    |  |      |  |   |

| A, B Source Address                     | 10                           | 12           | 0 (N     | ote 12)           | 21, 10 + t <sub>PV</sub> | 21, 10 + tpwL (Note 13)      |    | 0  |  |    |  |      |  |   |

| B Destination Address                   | 10                           | 12           | •        | Do N              | lot Change               |                              | 0  |    |  |    |  |      |  |   |

| Data                                    |                              | _            |          |                   | 1                        | .6                           | 0  |    |  |    |  |      |  |   |

| C <sub>n</sub>                          |                              |              |          | _                 | 1                        | 13                           | 0  |    |  |    |  |      |  |   |

| I <sub>012</sub>                        |                              |              |          | -                 | 1                        | 19 0                         |    | 0  |  |    |  |      |  |   |

| I <sub>345</sub>                        |                              |              |          |                   |                          |                              |    |    |  | 19 |  | - 19 |  | 0 |

| I <sub>678</sub>                        | 7                            | 9            | ♦ Do Not |                   | ot Change                | 0                            |    |    |  |    |  |      |  |   |

| RAM <sub>0, 3</sub> , Q <sub>0, 3</sub> |                              | <u> </u>     |          | _                 |                          | 9                            |    | 0  |  |    |  |      |  |   |

# Output Enable/Disable Times[2]

Output disable tests performed with  $C_L = 5 \text{ pF}$  and measured to 0.5V change of output voltage level.

| Device     | Input | Output | Enable | Disable |

|------------|-------|--------|--------|---------|

| CY7C901-23 | ŌĒ    | Y      | 14     | 16      |

| CY7C901-27 | ŌĒ    | Y      | 16     | 18      |

#### Notes:

- 10. A dash indicates a propagation delay path or set-up time constraint does not exist.

- 11. Certain signals must be stable during the entire clock LOW time to avoid erroneous operation. This is indicated by the phrase "do not change."

- 12. Source addresses must be stable prior to the clock H \( \phi \) L transition to allow time to access the source data before the latches close. The A address may then be changed. The B address can be changed if it is not

- a destination; i.e., if data is not being written back into the RAM. Normally A and B are not changed during the clock LOW time.

- 13. The set-up time prior to the clock L H transition is to allow time for data to be accessed, passed through the ALU, and returned to the RAM. It includes all the time from stable A and B addresses to the clock L H transition, regardless of when the clock H L transition occurs.

# CY7C901-31 Commercial and CY7C901-32 Military AC Performance Characteristics

The tables below specify the guaranteed AC performance of these devices over the commercial (0°C to 70°C) and military ( $-55^{\circ}\text{C}$  to  $+125^{\circ}\text{C}$ ) operating temperature range with  $V_{\text{CC}}$  varying from 4.5V to 5.5V. All times are in nanoseconds and are measured between the 1.5V signal levels. The inputs switch between 0V and 3V with signal transition rates of 1V per nanosecond. All outputs have maximum DC current loads. See "Electrical Characteristics" for loading circuit information.

This data applies to parts with the following numbers:

CY7C901-31PC CY7C901-31DC CY7C901-31LC

CY7C901-31JC CY7C901-32DMB CY7C901-32LMB

## Cycle Time and Clock Characteristics<sup>[2]</sup>

| CY7C901                                                                    | -31    | -32    |

|----------------------------------------------------------------------------|--------|--------|

| Read-Modify-Write Cycle (from selection of A, B registers to end of cycle) | 31 ns  | 32 ns  |

| Maximum Clock Frequency to shift Q (50% duty cycle, I = 432 or 632)        | 32 MHz | 31 MHz |

| Minimum Clock LOW Time                                                     | 16 ns  | 17 ns  |

| Minimum Clock HIGH Time                                                    | 15 ns  | 15 ns  |

| Minimum Clock Period                                                       | 31 ns  | 32 ns  |

For faster performance see CY7C901-23 specification on page 9.

# Combinatorial Propagation Delays (C<sub>L</sub> = 50 pF)[3, 10]

| To Output              | 1  | Y  | F        | 3              | C, | +4  | G, | , P | F: | = 0 | 0  | VR | RA | M <sub>0</sub> |          | 20 |

|------------------------|----|----|----------|----------------|----|-----|----|-----|----|-----|----|----|----|----------------|----------|----|

| From Input             | 1  | Y  | F        | <sup>7</sup> 3 | C. | + 4 | G, | , P | F: | = 0 | O  | VR | RA | М3             | (        | 23 |

| Speed (ns)             | 31 | 32 | 31       | 32             | 31 | 32  | 31 | 32  | 31 | 32  | 31 | 32 | 31 | 32             | 31       | 32 |

| A, B Address           | 40 | 48 | 40       | 48             | 40 | 48  | 37 | 44  | 40 | 48  | 40 | 48 | 40 | 48             | =        | =  |

| D                      | 30 | 37 | 30       | 37             | 30 | 37  | 30 | 34  | 38 | 40  | 30 | 37 | 30 | 37             | <u> </u> | _  |

| C <sub>n</sub>         | 22 | 25 | 22       | 25             | 20 | 21  | _  |     | 25 | 28  | 22 | 25 | 25 | 28             |          | =  |

| I <sub>012</sub>       | 35 | 40 | 35       | 40             | 35 | 40  | 37 | 44  | 37 | 44  | 35 | 40 | 35 | 40             |          | _  |

| I <sub>345</sub>       | 35 | 40 | 35       | 40             | 35 | 40  | 35 | 40  | 38 | 40  | 35 | 40 | 35 | 40             | -        |    |

| I <sub>678</sub>       | 25 | 29 |          |                | _  | _   |    | _   | _  |     | _  | _  | 26 | 29             | 26       | 29 |

| A Bypass ALU (I = 2XX) | 35 | 40 | <u> </u> | _              | _  | -   |    |     | _  |     | _  | _  | _  |                | =        | _  |

| Clock (LOW to HIGH)    | 35 | 40 | 35       | 40             | 35 | 40  | 35 | 40  | 35 | 40  | 35 | 40 | 35 | 40             | 28       | 33 |

# Set-Up and Hold Times Relative to Clock (CP) Input[3, 10, 11]

|                                         | CP:                         | _                        | 7                                      | <u> </u>                 |  |

|-----------------------------------------|-----------------------------|--------------------------|----------------------------------------|--------------------------|--|

|                                         | Set-Up Time<br>Before H ♦ L | Hold Time<br>After H ♦ L | Set-Up Time<br>Before L • H            | Hold Time<br>After L ♦ H |  |

| A, B Source Address                     | 15                          | 0<br>(Note 12)           | 30, 15 + t <sub>PWL</sub><br>(Note 13) | 0                        |  |

| B Destination Address                   | 15                          | ♦ Do No                  | t Change                               | 0                        |  |

| D                                       |                             | <del></del>              | 25                                     | 0                        |  |

| C <sub>n</sub>                          | _                           | _                        | 20                                     | 0                        |  |

| I <sub>012</sub>                        | _                           | <del></del>              | 30                                     | 0                        |  |

| I <sub>345</sub>                        |                             | <del></del>              | 30                                     | 0                        |  |

| I <sub>678</sub>                        | 10                          | ♦ Do No                  | t Change                               | 0                        |  |

| RAM <sub>0, 3</sub> , Q <sub>0, 3</sub> |                             | _                        | 12                                     | 0                        |  |

# Output Enable/Disable Times[2]

Output disable tests performed with  $C_L = 5 \, pF$  and measured to 0.5V change of output voltage level.

| Device     | Input | Output | Enable | Disable |

|------------|-------|--------|--------|---------|

| CY7C901-31 | ŌĒ    | Y      | 23     | 23      |

| CY7C901-32 | ŌĒ    | Y      | 25     | 25      |

# Minimum Cycle Time Calculations for 16-Bit Systems

Speed used in calculations for parts other than CY7C901 are representative for MSI parts.

Pipelined System, Add without Simultaneous Shift

|             | Data Loop                                        |       |         | Control Loop     |       |

|-------------|--------------------------------------------------|-------|---------|------------------|-------|

| CY7C245     | Clock to Output                                  | 12    | CY7C245 | Clock to Output  | 12    |

| CY7C901     | A. B to G, P                                     | 28    | MUX     | Select to Output | 12    |

| Carry Logic | $\overline{G}_0$ , $\overline{P}_0$ to $C_{n+Z}$ | 9     | CY7C901 | CC to Output     | 22    |

| CY7C901     | C <sub>n</sub> to Worst Case                     | 18    | CY7C245 | Access Time      | 20    |

| Register    | Set-Up                                           | 4     |         |                  | 66 ns |

| U           | -                                                | 71 ns |         |                  |       |

#### Minimum Clock Period = 71 ns

Pipelined System, Simultaneous Add and Shift Down (RIGHT)

|             | Data Loop                                        |       |         | Control Loop     |       |

|-------------|--------------------------------------------------|-------|---------|------------------|-------|

| CY7C245     | Clock to Output                                  | 12    | CY7C245 | Clock to Output  | 12    |

| CY7C901     | A, B to $\overline{G}$ , $\overline{P}$          | 28    | MUX     | Select to Output | 12    |

| Carry Logic | $\overline{G}_0$ , $\overline{P}_0$ to $C_{n+Z}$ | 9     | CY7C901 | CC to Output     | 22    |

| CY7C901     | C <sub>n</sub> to Worst Case                     | 18    | CY7C245 | Access Time      | 20    |

| XOR and MUX | Prop. Delay, Select to<br>Output                 | 20    |         |                  | 66 ns |

| CY7C901     | RAM <sub>3</sub> Setup                           | 9     |         |                  |       |

|             | •                                                | 96 ns |         |                  |       |

Minimum Clock Period = 96 ns

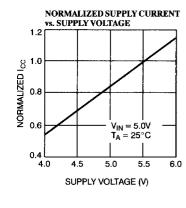

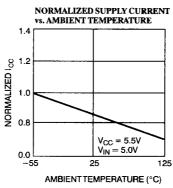

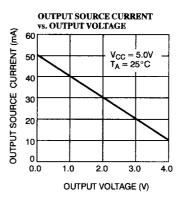

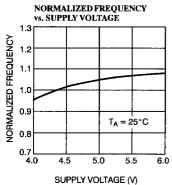

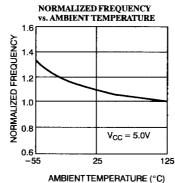

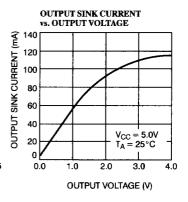

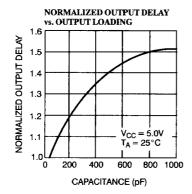

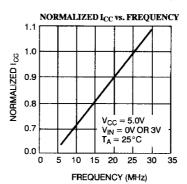

## Typical DC and AC Characteristics

7C901-9

# **Ordering Information**

| Read-<br>Modify-<br>Write Cycle<br>(ns) | Ordering Code | Package<br>Type | Operating<br>Range |

|-----------------------------------------|---------------|-----------------|--------------------|

| 23                                      | CY7C901-23DC  | D18             | Commercial         |

|                                         | CY7C901-23JC  | J67             |                    |

| ļ                                       | CY7C901-23LC  | L67             |                    |

|                                         | CY7C901-23PC  | P17             |                    |

| 27                                      | CY7C901-27DMB | D18             | Military           |

|                                         | CY7C901-27LMB | L67             | l                  |

| 31                                      | CY7C901-31DC  | D18             | Commercial         |

|                                         | CY7C901-31JC  | J67             |                    |

|                                         | CY7C901-31LC  | L67             |                    |

| ĺ                                       | CY7C901-31PC  | P17             | ]                  |

| 32                                      | CY7C901-32DMB | D18             | Military           |

|                                         | CY7C901-32LMB | L67             | <u> </u>           |

# MILITARY SPECIFICATIONS Group A Subgroup Testing

# **DC** Characteristics

| Parameters           | Subgroups |

|----------------------|-----------|

| V <sub>OH</sub>      | 1, 2, 3   |

| V <sub>OL</sub>      | 1, 2, 3   |

| V <sub>IH</sub>      | 1, 2, 3   |

| V <sub>IL</sub> Max. | 1, 2, 3   |

| $I_{IX}$             | 1, 2, 3   |

| I <sub>OZ</sub>      | 1, 2, 3   |

| I <sub>SC</sub>      | 1, 2, 3   |

| $I_{CC}$             | 1, 2, 3   |

| I <sub>CC1</sub>     | 1, 2, 3   |

# **Cycle Time and Clock Characteristics**

| Parameters              | Subgroups       |  |

|-------------------------|-----------------|--|

| Minimum Clock LOW Time  | 7, 8, 9, 10, 11 |  |

| Minimum Clock HIGH Time | 7, 8, 9, 10, 11 |  |

# **Combinational Propagation Delays**

| Parameters                                               | Subgroups       |

|----------------------------------------------------------|-----------------|

| From A, B Address to Y                                   | 7, 8, 9, 10, 11 |

| From A, B Address to F <sub>3</sub>                      | 7, 8, 9, 10, 11 |

| From A, B Address to C <sub>n+4</sub>                    | 7, 8, 9, 10, 11 |

| From A, B Address to $\overline{G}$ , $\overline{P}$     | 7, 8, 9, 10, 11 |

| From A, B Address to $F = 0$                             | 7, 8, 9, 10, 11 |

| From A, B Address to OVR                                 | 7, 8, 9, 10, 11 |

| From A, B Address to RAM <sub>0, 3</sub>                 | 7, 8, 9, 10, 11 |

| From D to Y                                              | 7, 8, 9, 10, 11 |

| From D to F <sub>3</sub>                                 | 7, 8, 9, 10, 11 |

| From D to C <sub>n+4</sub>                               | 7, 8, 9, 10, 11 |

| From D to G, P                                           | 7, 8, 9, 10, 11 |

| From D to $F = 0$                                        | 7, 8, 9, 10, 11 |

| From D to OVR                                            | 7, 8, 9, 10, 11 |

| From D to RAM <sub>0, 3</sub>                            | 7, 8, 9, 10, 11 |

| From C <sub>n</sub> to Y                                 | 7, 8, 9, 10, 11 |

| From C <sub>n</sub> to F <sub>3</sub>                    | 7, 8, 9, 10, 11 |

| From $C_n$ to $C_{n+4}$                                  | 7, 8, 9, 10, 11 |

| From $C_n$ to $F = 0$                                    | 7, 8, 9, 10, 11 |

| From C <sub>n</sub> to OVR                               | 7, 8, 9, 10, 11 |

| From C <sub>n</sub> to RAM <sub>0, 3</sub>               | 7, 8, 9, 10, 11 |

| From I <sub>012</sub> to Y                               | 7, 8, 9, 10, 11 |

| From I <sub>012</sub> to F <sub>3</sub>                  | 7, 8, 9, 10, 11 |

| From I <sub>012</sub> to C <sub>n + 4</sub>              | 7, 8, 9, 10, 11 |

| From I <sub>012</sub> to $\overline{G}$ , $\overline{P}$ | 7, 8, 9, 10, 11 |

| From $I_{012}$ to $F = 0$                                | 7, 8, 9, 10, 11 |

| From I <sub>012</sub> to OVR                             | 7, 8, 9, 10, 11 |

| From I <sub>012</sub> to RAM <sub>0, 3</sub>             | 7, 8, 9, 10, 11 |

# Combinational Propagation Delays (continued)

| Parameters                                                | Subgroups       |  |

|-----------------------------------------------------------|-----------------|--|

| From I <sub>345</sub> to Y                                | 7, 8, 9, 10, 11 |  |

| From I <sub>345</sub> to F <sub>3</sub>                   | 7, 8, 9, 10, 11 |  |

| From I <sub>345</sub> to C <sub>n+4</sub>                 | 7, 8, 9, 10, 11 |  |

| From I <sub>345</sub> to $\overline{G}$ , $\overline{P}$  | 7, 8, 9, 10, 11 |  |

| From $I_{345}$ to $F = 0$                                 | 7, 8, 9, 10, 11 |  |

| From I <sub>345</sub> to OVR                              | 7, 8, 9, 10, 11 |  |

| From I <sub>345</sub> to RAM <sub>0, 3</sub>              | 7, 8, 9, 10, 11 |  |

| From I <sub>678</sub> to Y                                | 7, 8, 9, 10, 11 |  |

| From I <sub>678</sub> to RAM <sub>0, 3</sub>              | 7, 8, 9, 10, 11 |  |

| From I <sub>678</sub> to Q <sub>0, 3</sub>                | 7, 8, 9, 10, 11 |  |

| From A Bypass ALU to Y $(I = 2XX)$                        | 7, 8, 9, 10, 11 |  |

| From Clock LOW to HIGH to Y                               | 7, 8, 9, 10, 11 |  |

| From Clock LOW to HIGH to F <sub>3</sub>                  | 7, 8, 9, 10, 11 |  |

| From Clock LOW to HIGH to C <sub>n+4</sub>                | 7, 8, 9, 10, 11 |  |

| From Clock LOW to HIGH to $\overline{G}$ , $\overline{P}$ | 7, 8, 9, 10, 11 |  |

| From Clock LOW to HIGH to $F = 0$                         | 7, 8, 9, 10, 11 |  |

| From Clock LOW to HIGH to OVR                             | 7, 8, 9, 10, 11 |  |

| From Clock LOW to HIGH to RAM <sub>0, 3</sub>             | 7, 8, 9, 10, 11 |  |

| From Clock LOW to HIGH to Q <sub>0, 3</sub>               | 7, 8, 9, 10, 11 |  |

Set-Up and Hold Times Relative to Clock (CP) Input

| · · · · · · · · · · · · · · · · ·                                                                 | · · · · ·       |

|---------------------------------------------------------------------------------------------------|-----------------|

| Parameters                                                                                        | Subgroups       |

| A, B Source Address<br>Set-Up Time Before H ▶ L                                                   | 7, 8, 9, 10, 11 |

| A, B Source Address<br>Hold Time After H ≱ L                                                      | 7, 8, 9, 10, 11 |

| A, B Source Address<br>Set-Up Time Before L ▶ H                                                   | 7, 8, 9, 10, 11 |

| A, B Source Address<br>Hold Time After L ♦ H                                                      | 7, 8, 9, 10, 11 |

| B Destination Address<br>Set-Up Time Before H ▶ L                                                 | 7, 8, 9, 10, 11 |

| B Destination Address<br>Hold Time After H ♦ L                                                    | 7, 8, 9, 10, 11 |

| B Destination Address<br>Set-Up Time Before L ▶ H                                                 | 7, 8, 9, 10, 11 |

| B Destination Address<br>Hold Time After L ♦ H                                                    | 7, 8, 9, 10, 11 |

| D Set-Up Time Before L ♦ H                                                                        | 7, 8, 9, 10, 11 |

| D Hold Time After L ♦ H                                                                           | 7, 8, 9, 10, 11 |

| C <sub>n</sub> Set-Up Time Before L ♦ H                                                           | 7, 8, 9, 10, 11 |

| C <sub>n</sub> Hold Time After L ♦ H                                                              | 7, 8, 9, 10, 11 |

| I <sub>012</sub> Set-Up Time Before L → H                                                         | 7, 8, 9, 10, 11 |

| I <sub>012</sub> Hold Time After L ♦ H                                                            | 7, 8, 9, 10, 11 |

| I <sub>345</sub> Set-Up Time Before L ♦ H                                                         | 7, 8, 9, 10, 11 |

| I <sub>345</sub> Hold Time After L ♦ H                                                            | 7, 8, 9, 10, 11 |

| I <sub>678</sub> Set-Up Time Before H ♦ L                                                         | 7, 8, 9, 10, 11 |

| I <sub>678</sub> Hold Time After H ♦ L                                                            | 7, 8, 9, 10, 11 |

| I <sub>678</sub> Set-Up Time Before L ♦ H                                                         | 7, 8, 9, 10, 11 |

| I <sub>678</sub> Hold Time After L ♦ H                                                            | 7, 8, 9, 10, 11 |

| RAM <sub>0</sub> , RAM <sub>3</sub> , Q <sub>0</sub> , Q <sub>3</sub><br>Set-Up Time Before L ♦ H | 7, 8, 9, 10, 11 |

| RAM <sub>0</sub> , RAM <sub>3</sub> , Q <sub>0</sub> , Q <sub>3</sub><br>Hold Time After L ♦ H    | 7, 8, 9, 10, 11 |

Document #: 38-00021-B