## National Semiconductor is now part of Texas Instruments.

Search <a href="http://www.ti.com/">http://www.ti.com/</a> for the latest technical information and details on our current products and services.

### Semiconductor DS90UR903Q/DS90UR904Q

### 10 - 43MHz 18 Bit Color FPD-Link II Serializer and Deserializer

#### **General Description**

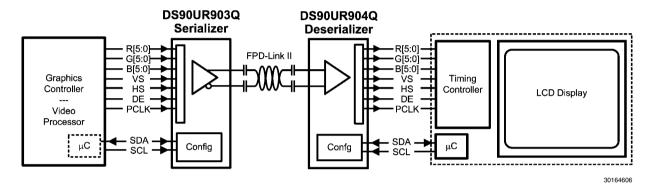

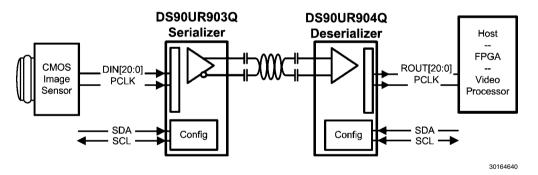

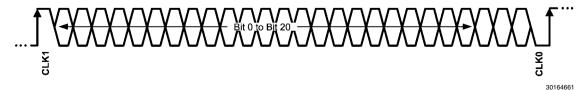

The DS90UR903Q/DS90UR904Q chipset offers a FPD-Link Il interface with a high-speed forward channel for data transmission over a single differential pair. The Serializer/ Deserializer pair is targeted for direct connections between graphics host controller and displays modules. This chipset is ideally suited for driving video data to displays requiring 18-bit color depth (RGB666 + HS. VS. and DE). The serializer converts 21 bit data over a single high-speed serial stream. This single serial stream simplifies transferring a wide data bus over PCB traces and cable by eliminating the skew problems between parallel data and clock paths. This significantly saves system cost by narrowing data paths that in turn reduce PCB layers, cable width, and connector size and pins.

The Deserializer inputs provide equalization control to compensate for loss from the media over longer distances. Internal DC balanced encoding/decoding is used to support AC-Coupled interconnects.

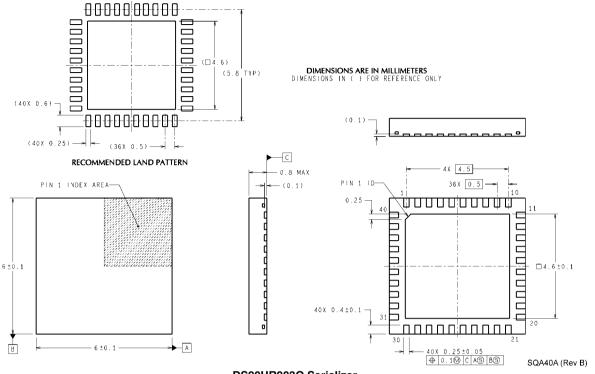

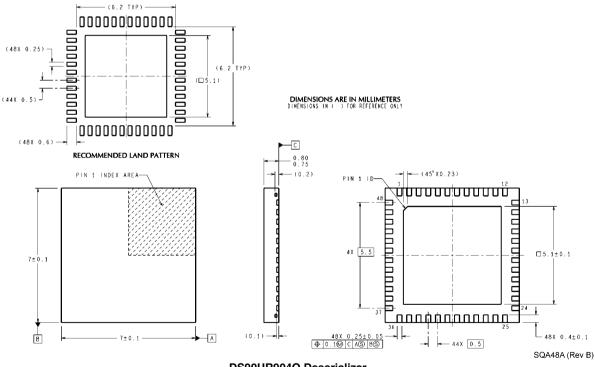

The Serializer is offered in a 40-pin lead in LLP and Deserializer is offered in a 48-pin LLP packages.

#### **Features**

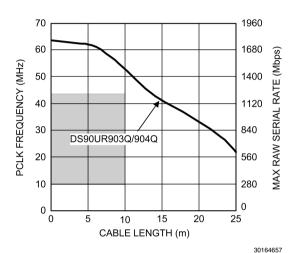

- 10 MHz to 43 MHz input PCLK support

- 210 Mbps to 903 Mbps data throughput

- Single differential pair interconnect

- Embedded clock with DC Balanced coding to support ACcoupled interconnects

- Capable to drive up to 10 meters shielded twisted-pair

- I<sup>2</sup>C compatible serial interface for device configuration

- Single hardware device addressing pin

- LOCK output reporting pin to validate link integrity

- Integrated termination resistors

- 1.8V- or 3.3V-compatible parallel bus interface

- Single power supply at 1.8V

- ISO 10605 ESD and IEC 61000-4-2 ESD compliant

- Automotive grade product: AEC-Q100 Grade 2 qualified

- Temperature range -40°C to +105°C

- No reference clock required on Deserializer

- Programmable Receive Equalization

- **EMI/EMC Mitigation**

- DES Programmable Spread Spectrum (SSCG) outputs

- DES Receiver staggered outputs

#### **Applications**

- Automotive Display Systems

- Central Information Displays

- Navigation Displays

- Rear Seat Entertainment

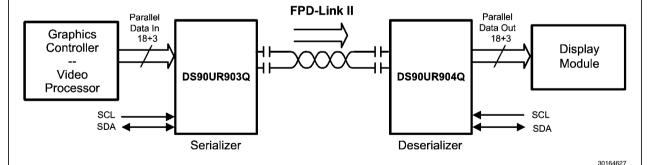

### Typical Application Diagram

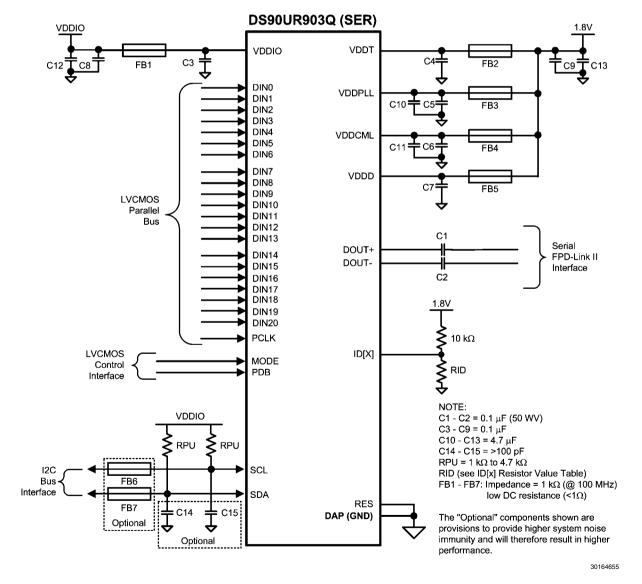

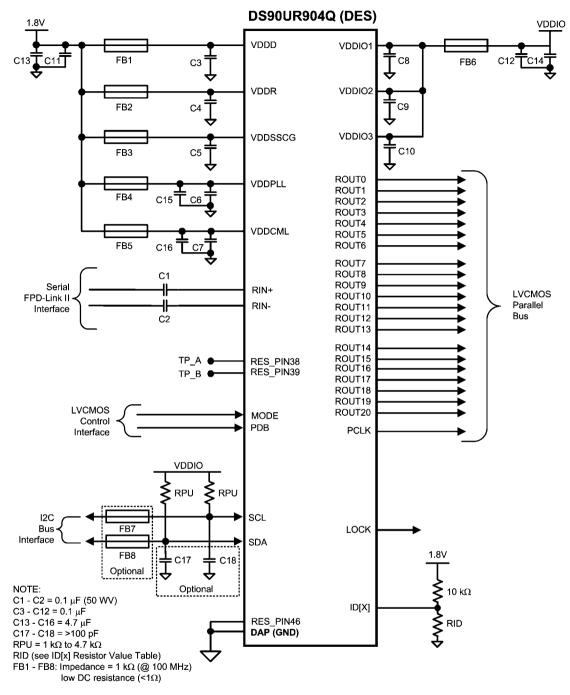

FIGURE 1. Typical Application Circuit

TRI-STATE® is a registered trademark of National Semiconductor Corporation.

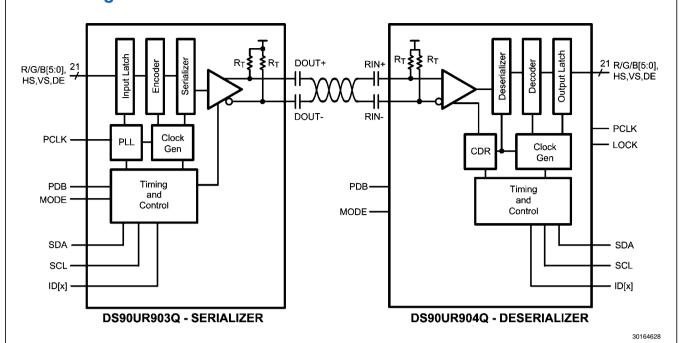

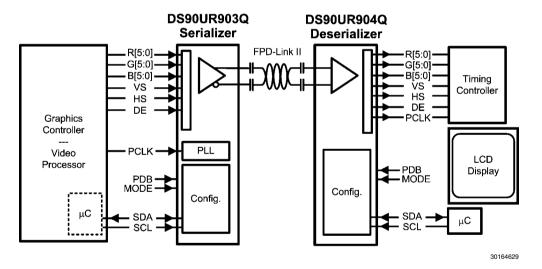

### **Block Diagrams**

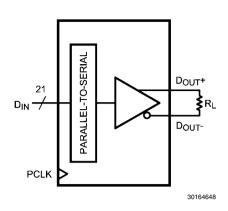

FIGURE 2. Block Diagram

FIGURE 3. Application Block Diagram

### **Ordering Information**

| NSID          | Package Description                          | Quantity | SPEC | Package ID |

|---------------|----------------------------------------------|----------|------|------------|

| DS90UR903QSQE | 40-pin LLP, 6.0 X 6.0 X 0.8 mm, 0.5 mm pitch | 250      | NOPB | SQA40A     |

| DS90UR903QSQ  | 40-pin LLP, 6.0 X 6.0 X 0.8 mm, 0.5 mm pitch | 1000     | NOPB | SQA40A     |

| DS90UR903QSQX | 40-pin LLP, 6.0 X 6.0 X 0.8 mm, 0.5 mm pitch | 4500     | NOPB | SQA40A     |

| DS90UR904QSQE | 48-pin LLP, 7.0 X 7.0 X 0.8 mm, 0.5 mm pitch | 250      | NOPB | SQA48A     |

| DS90UR904QSQ  | 48-pin LLP, 7.0 X 7.0 X 0.8 mm, 0.5 mm pitch | 1000     | NOPB | SQA48A     |

| DS90UR904QSQX | 48-pin LLP, 7.0 X 7.0 X 0.8 mm, 0.5 mm pitch | 4500     | NOPB | SQA48A     |

Note: Automotive Grade (Q) product incorporates enhanced manufacturing and support processes for the automotive market, including defect detection methodologies. Reliability qualification is compliant with the requirements and temperature grades defined in the AEC Q100 standard. Automotive Grade products are identified with the letter Q. For more information go to http://www.national.com/automotive.

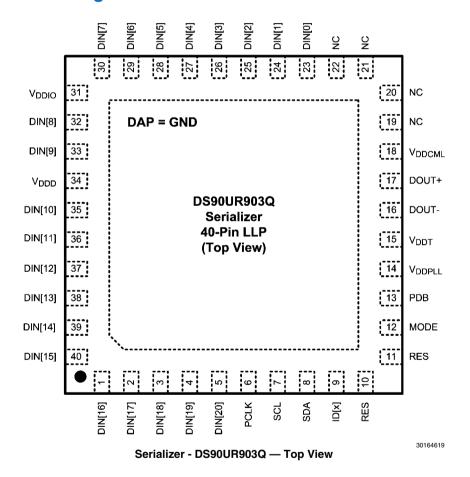

### **DS90UR903Q Pin Diagram**

### **DS90UR903Q Serializer Pin Descriptions**

| Pin Name       | Pin No.                                                                                   | I/O, Type                     | Description                                                                                                                                                                                                                                                                      |

|----------------|-------------------------------------------------------------------------------------------|-------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LVCMOS PARA    | ALLEL INTERFA                                                                             | CE                            |                                                                                                                                                                                                                                                                                  |

| DIN[20:0]      | 5, 4, 3, 2, 1,<br>40, 39, 38, 37,<br>36, 35, 33, 32,<br>30, 29, 28, 27,<br>26, 25, 24, 23 | w/ pull down                  | Parallel data inputs.                                                                                                                                                                                                                                                            |

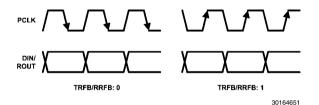

| PCLK           | 6                                                                                         | Input, LVCMOS<br>w/ pull down | Pixel Clock Input Pin. Strobe edge set by TRFB control register.                                                                                                                                                                                                                 |

| SERIAL CONT    | ROL BUS - I <sup>2</sup> C (                                                              | COMPATIBLE                    |                                                                                                                                                                                                                                                                                  |

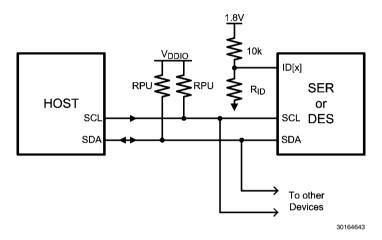

| SCL            | 7                                                                                         | Input,<br>Open Drain          | Clock line for the serial control bus communication SCL requires an external pull-up resistor to V <sub>DDIO</sub> .                                                                                                                                                             |

| SDA            | 8                                                                                         | Input/Output,<br>Open Drain   | Data line for the serial control bus communication SDA requires an external pull-up resistor to V <sub>DDIO</sub> .                                                                                                                                                              |

| MODE           | 12                                                                                        | Input, LVCMOS<br>w/ pull down | I <sup>2</sup> C Mode select MODE = H,- <b>REQUIRED</b> . The MODE pin must be set HIGH to allow I <sup>2</sup> C configuration of the serializer.                                                                                                                               |

| ID[x]          | 9                                                                                         | Input, analog                 | Device ID Address Select Resistor to Ground and 10 $k\Omega$ pull-up to 1.8V rail. See <i>Table 3</i>                                                                                                                                                                            |

| CONTROL ANI    | CONFIGURAT                                                                                | ION                           |                                                                                                                                                                                                                                                                                  |

| PDB            | 13                                                                                        | Input, LVCMOS<br>w/ pull down | Power down Mode Input Pin.  PDB = H, Serializer is enabled and is ON.  PDB = L, Serailizer is in Power Down mode. When the Serializer is in Power Down, the PLL is shutdown, and IDD is minimized. Programmed control register data are NOT retained and reset to default values |

| RES            | 10, 11                                                                                    | Input, LVCMOS<br>w/ pull down | Reserved. This pin MUST be tied LOW.                                                                                                                                                                                                                                             |

| NC             | 22, 21, 20, 19                                                                            |                               | No Connect                                                                                                                                                                                                                                                                       |

| FPD-LINK II IN | TERFACE                                                                                   |                               |                                                                                                                                                                                                                                                                                  |

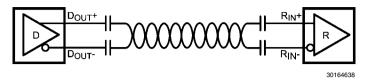

| DOUT+          | 17                                                                                        | Output, CML                   | Non-inverting differential output. The interconnect must be AC Coupled with a 100 nF capacitor.                                                                                                                                                                                  |

| DOUT-          | 16                                                                                        | Output, CML                   | Inverting differential output. The interconnect must be AC Coupled with a 100 nF capacitor.                                                                                                                                                                                      |

| POWER AND O    | GROUND                                                                                    |                               |                                                                                                                                                                                                                                                                                  |

| VDDPLL         | 14                                                                                        | Power, Analog                 | PLL Power, 1.8V ±5%                                                                                                                                                                                                                                                              |

| VDDT           | 15                                                                                        | Power, Analog                 | Tx Analog Power, 1.8V ±5%                                                                                                                                                                                                                                                        |

| VDDCML         | 18                                                                                        | Power, Analog                 | CML Power, 1.8V ±5%                                                                                                                                                                                                                                                              |

| VDDD           | 34                                                                                        | Power, Digital                | Digital Power, 1.8V ±5%                                                                                                                                                                                                                                                          |

| VDDIO          | 31                                                                                        | Power, Digital                | Power for I/O stage. The single-ended inputs and SDA, SCL are powered from $V_{DDIO}$ . $V_{DDIO}$ can be connected to a 1.8V ±5% or 3.3V ±10%                                                                                                                                   |

| VSS            | DAP                                                                                       | Ground, DAP                   | DAP must be grounded. DAP is the large metal contact at the bottom side, located at the center of the LLP package. Connected to the ground plane (GND) with at least 16 vias.                                                                                                    |

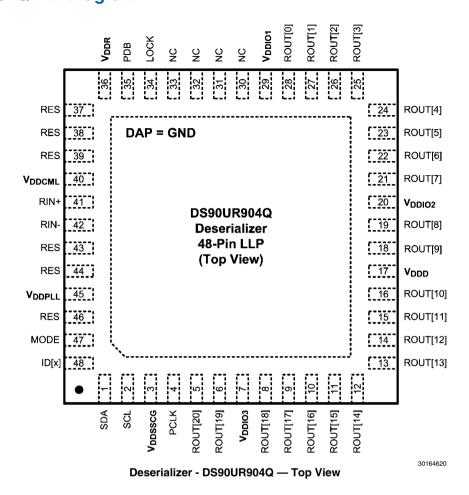

### **DS90UR904Q Pin Diagram**

5

### **DS90UR904Q Deserializer Pin Descriptions**

| Pin Name       | Pin No.                      | I/O, Type         | Description                                                                                   |

|----------------|------------------------------|-------------------|-----------------------------------------------------------------------------------------------|

| LVCMOS PAR     | ALLEL INTERFA                | ACE               |                                                                                               |

| ROUT[20:0]     | 5, 6, 8, 9, 10,              | Outputs,          | Parallel data outputs.                                                                        |

|                | 11, 12, 13, 14,              |                   | ·                                                                                             |

|                | 15, 16, 18, 19,              |                   |                                                                                               |

|                | 21, 22, 23, 24,              |                   |                                                                                               |

|                | 25, 26, 27, 28               |                   |                                                                                               |

| PCLK           | 4                            | Output,<br>LVCMOS | Pixel Clock Output Pin. Strobe edge set by RRFB control register.                             |

| SERIAL CONT    | ROL BUS - I <sup>2</sup> C ( | COMPATIBLE        |                                                                                               |

|                |                              | Input,            | Clock line for the serial control bus communication                                           |

| SCL            | 2                            | Open Drain        | SCL requires an external pull-up resistor to V <sub>DDIO</sub> .                              |

|                |                              | Input/Output,     | Data line for the serial control bus communication                                            |

| SDA            | 1                            | Open Drain        | SDA requires an external pull-up resistor to V <sub>DDIO</sub> .                              |

|                |                              | Open Brain        | I2C Mode select                                                                               |

|                |                              |                   |                                                                                               |

| MODE           | 47                           | Input, LVCMOS     | MODE = H - REQUIRED. The MODE pin must be set HIGH to allow I <sup>2</sup> C configuration    |

|                |                              | w/ pull up        | of the deserializer.                                                                          |

|                | +                            |                   | Device ID Address Select                                                                      |

| ID[x]          | 48                           | Input, analog     | Resistor to Ground and 10 k $\Omega$ pull-up to 1.8V rail. See <i>Table 4</i>                 |

| CONTROL AN     | │<br>D CONFIGURAT            | ION               | Thesistor to Ground and To K22 pull-up to 1.0V fail. See Table 4                              |

| CONTINUE AN    |                              |                   | Power down Mode Input Pin.                                                                    |

|                |                              |                   | PDB = H, Deserializer is enabled and is ON.                                                   |

| PDB            | 35                           | Input, LVCMOS     | PDB = L, Deserializer is in Power Down mode. When the Deserializer is in Power                |

| FDB            | 35                           | w/ pull down      |                                                                                               |

|                |                              |                   | Down. Programmed control register data are NOT retained and reset to default values.          |

|                |                              |                   | 11.1.1.1                                                                                      |

|                |                              |                   | LOCK Status Output Pin.                                                                       |

| LOCK           | 34                           | Output,           | LOCK = H, PLL is Locked, outputs are active                                                   |

|                |                              | LVCMOS            | LOCK = L, PLL is unlocked, ROUT and PCLK output states are controlled by                      |

|                |                              |                   | OSS_SEL control register. May be used as Link Status.                                         |

|                |                              |                   | Reserved.                                                                                     |

| RES            | 37, 38, 39, 43,              | -                 | Pin 46: This pin MUST be tied LOW.                                                            |

|                | 44, 46                       |                   | Pin 37, 43, 44: Leave pin open.                                                               |

|                |                              |                   | Pins 38, 39: Route to test point or leave open if unused.                                     |

| NC             | 30, 31, 32, 33               |                   | No Connect                                                                                    |

| FPD-LINK II IN | TERFACE                      |                   |                                                                                               |

| RIN+           | 41                           | Input, CML        | Noninverting differential input. The interconnect must be AC Coupled with a 100 nF capacitor. |

| RIN-           | 42                           | Inputt, CML       | Inverting differential input. The interconnect must be AC Coupled with a 100 nF capacitor.    |

| Pin Name    | Pin No.   | I/O, Type      | Description                                                                                                                                                                   |

|-------------|-----------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| POWER AND G | ROUND     |                |                                                                                                                                                                               |

| VDDSSCG     | 3         | Power, Digital | SSCG Power, 1.8V ±5% Power supply must be connected regardless if SSCG function is in operation.                                                                              |

| VDDIO1/2/3  | 29, 20, 7 | Power, Digital | LVCMOS I/O Buffer Power, The single-ended outputs and control input are powered from $V_{DDIO}$ . $V_{DDIO}$ can be connected to a 1.8V ±5% or 3.3V ±10%                      |

| VDDD        | 17        | Power, Digital | Digital Core Power, 1.8V ±5%                                                                                                                                                  |

| VDDR        | 36        | Power, Analog  | Rx Analog Power, 1.8V ±5%                                                                                                                                                     |

| VDDCML      | 40        | Power, Analog  | 1.8V ±5%                                                                                                                                                                      |

| VDDPLL      | 45        | Power, Analog  | PLL Power, 1.8V ±5%                                                                                                                                                           |

| VSS         | DAP       | Ground, DAP    | DAP must be grounded. DAP is the large metal contact at the bottom side, located at the center of the LLP package. Connected to the ground plane (GND) with at least 16 vias. |

#### **Absolute Maximum Ratings** (Note 1)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/Distributors for availability and specifications.

Supply Voltage - V $_{\rm DDn}$  (1.8V) -0.3V to +2.5V Supply Voltage - V $_{\rm DDIO}$  -0.3V to +4.0V LVCMOS Input Voltage I/O Voltage -0.3V to + (VDDIO +0.3V) CML Driver I/O Voltage (V $_{\rm DD}$ ) -0.3V to + (V $_{\rm DD}$  +0.3V) CML Receiver I/O Voltage (V $_{\rm DD}$ ) -0.3V to (V $_{\rm DD}$  +0.3V)

Junction Temperature +150°C

Storage Temperature -65°C to +150°C

Maximum Package Power

Dissipation Capacity Package 1/θ<sub>JA</sub> °C/W above +25° Package Derating: DS90UR903Q 40L LLP

$\theta_{\rm JA}$  30.7 °C/W (based on 16 thermal vias)  $\theta_{\rm JC}$  6.8 °C/W (based on 16 thermal vias) DS90UR904Q 48L LLP  $\theta_{\rm JA}$  26.9 °C/W (based on 16 thermal vias)  $\theta_{\rm JC}$  4.4 °C/W (based on 16 thermal vias)

Contact Discharge

(DOUT+, DOUT-, RIN+, RIN-)  $\geq \pm 10 \text{ kV}$ ESD Rating (ISO10605)  $R_D = 330\Omega$ ,  $C_S = 150/330 \text{pF}$

| ESD Rating (ISO10605)                        | $R_D = 2K\Omega, C_S = 150/330pF$ |

|----------------------------------------------|-----------------------------------|

| Air Discharge<br>(DOUT+, DOUT-, RIN+, RIN-)  | ≥±15 kV                           |

| Contact Discharge (DOUT+, DOUT-, RIN+, RIN-) | ≥±10 kV                           |

| ESD Rating (HBM)                             | ≥±8 kV                            |

| ESD Rating (CDM)                             | ≥±1 kV                            |

| ESD Rating (MM)                              | ≥±250 V                           |

For soldering specifications:

see product folder at www.national.com and www.national.com/ms/MS/MS-SOLDERING.pdf

# Recommended Operating Conditions

|                                    | Min  | Nom | Max  | Units |

|------------------------------------|------|-----|------|-------|

| Supply Voltage                     | 1.71 | 1.8 | 1.89 | V     |

| (V <sub>DDn</sub> )                |      |     |      |       |

| LVCMOS Supply                      | 1.71 | 1.8 | 1.89 | V     |

| Voltage (V <sub>DDIO</sub> )<br>OR |      |     |      |       |

| LVCMOS Supply                      | 3.0  | 3.3 | 3.6  | V     |

| Voltage (V <sub>DDIO</sub> )       |      |     |      | -     |

| Supply Noise                       |      |     |      |       |

| V <sub>DDn</sub> (1.8V)            |      |     | 25   | mVp-p |

| V <sub>DDIO</sub> (1.8V)           |      |     | 25   | mVp-p |

| V <sub>DDIO</sub> (3.3V)           |      |     | 50   | mVp-p |

| Operating Free Air                 | -40  | +25 | +105 | °C    |

| Temperature (T <sub>A</sub> )      | 40   | 120 | +105 | O     |

| PCLK Clock                         | 10   |     | 43   | MHz   |

| Frequency                          |      |     |      |       |

| Frequency                          |      |     |      |       |

#### **Electrical Characteristics** (Note 2, Note 3, Note 4)

Over recommended operating supply and temperature ranges unless otherwise specified.

≥±10 kV

| Symbol          | Parameter                    | Conditions                                                         | Min                  | Тур     | Max                  | Units |

|-----------------|------------------------------|--------------------------------------------------------------------|----------------------|---------|----------------------|-------|

| LVCMOS          | DC SPECIFICATIONS 3.3V I/O   | (SER INPUTS, DES OUTPUTS, CO                                       | ONTROL INPUTS AND    | OUTPUTS | S)                   |       |

| V <sub>IH</sub> | High Level Input Voltage     | V <sub>IN</sub> = 3.0V to 3.6V                                     | 2.0                  |         | V <sub>IN</sub>      | ٧     |

| V <sub>IL</sub> | Low Level Input Voltage      | V <sub>IN</sub> = 3.0V to 3.6V                                     | GND                  |         | 0.8                  | ٧     |

| I <sub>IN</sub> | Input Current                | $V_{IN} = 0V \text{ or } 3.6V$<br>$V_{IN} = 3.0V \text{ to } 3.6V$ | -20                  | ±1      | +20                  | μΑ    |

| V <sub>OH</sub> | High Level Output Voltage    | $V_{DDIO} = 3.0V \text{ to } 3.6V$<br>$I_{OH} = -4 \text{ mA}$     | 2.4                  |         | V <sub>DDIO</sub>    | V     |

| V <sub>OL</sub> | Low Level Output Voltage     | $V_{DDIO} = 3.0V \text{ to } 3.6V$<br>$I_{OL} = +4 \text{ mA}$     | GND                  |         | 0.4                  | V     |

| I <sub>os</sub> | Output Short Circuit Current | V <sub>OUT</sub> = 0V                                              |                      | -39     |                      | mA    |

| l <sub>oz</sub> | TRI-STATE® Output Current    | $PDB = 0V,$ $V_{OUT} = 0V \text{ or } V_{DD}$                      | -20                  | ±1      | +20                  | μΑ    |

| LVCMOS          | DC SPECIFICATIONS 1.8V I/0   | (SER INPUTS, DES OUTPUTS, CO                                       | ONTROL INPUTS AND    | OUTPUTS | S)                   |       |

| V <sub>IH</sub> | High Level Input Voltage     | V <sub>IN</sub> = 1.71V to 1.89V                                   | 0.65 V <sub>IN</sub> |         | V <sub>IN</sub> +0.3 | V     |

| V <sub>IL</sub> | Low Level Input Voltage      | V <sub>IN</sub> = 1.71V to 1.89V                                   | GND                  |         | 0.35 V <sub>IN</sub> | V     |

| I <sub>IN</sub> | Input Current                | V <sub>IN</sub> = 0V or 1.89V<br>V <sub>IN</sub> = 1.71V to 1.89V  | -20                  | ±1      | +20                  | μΑ    |

| Symbol              | Parameter                                                    | Condition                                                        | ns                                                  | Min                                           | Тур                               | Max                                           | Units |

|---------------------|--------------------------------------------------------------|------------------------------------------------------------------|-----------------------------------------------------|-----------------------------------------------|-----------------------------------|-----------------------------------------------|-------|

| V <sub>OH</sub>     | High Level Output Voltage                                    | $V_{DDIO} = 1.71V \text{ to } 1.89V$<br>$I_{OH} = -4 \text{ mA}$ |                                                     | V <sub>DDIO</sub> -<br>0.45                   |                                   | V <sub>DDIO</sub>                             | V     |

| V <sub>OL</sub>     | Low Level Output Voltage                                     | $V_{DDIO} = 1.71V \text{ to } 1.89V$                             |                                                     | CND                                           |                                   | 0.45                                          | V     |

|                     |                                                              | $I_{OL} = +4 \text{ mA}$                                         |                                                     | GND                                           |                                   | 0.45                                          | V     |

| I <sub>os</sub>     | Output Short Circuit Current                                 | $V_{OUT} = 0V$                                                   |                                                     |                                               | -20                               |                                               | mA    |

| I <sub>OZ</sub>     | TRI-STATE® Output Current                                    | PDB = 0V,<br>$V_{OUT} = 0V \text{ or } V_{DD}$                   |                                                     | -20                                           | ±1                                | +20                                           | μΑ    |

| CML DRIV            | ER DC SPECIFICATIONS (DO                                     | OUT+, DOUT-)                                                     |                                                     | •                                             |                                   | ,                                             |       |

| IV <sub>OD</sub> I  | Output Differential Voltage                                  | $R_T = 100\Omega (Figure 7)$                                     |                                                     | 268                                           | 340                               | 412                                           | mV    |

| ΔV <sub>OD</sub>    | Output Differential Voltage<br>Unbalance                     | $R_L = 100\Omega$                                                |                                                     |                                               | 1                                 | 50                                            | mV    |

| V <sub>OS</sub>     | Output Differential Offset<br>Voltage                        | $R_L = 100\Omega$ (Figure 7)                                     |                                                     | V <sub>DD (MIN)</sub> - V <sub>OD (MAX)</sub> | V <sub>DD</sub> - V <sub>OD</sub> | V <sub>DD (MAX)</sub> - V <sub>OD (MIN)</sub> | V     |

| ΔV <sub>OS</sub>    | Offset Voltage Unbalance                                     | $R_1 = 100\Omega$                                                |                                                     | OD (MAX)                                      | 1                                 | 50                                            | mV    |

| I <sub>os</sub>     | Output Short Circuit Current                                 | DOUT+/- = 0V                                                     |                                                     |                                               | -27                               |                                               | mA    |

| R <sub>T</sub>      | Differential Internal Termination Resistance                 | Differential across DOUT+                                        | 80                                                  | 100                                           | 120                               | Ω                                             |       |

| CML REC             | EIVER DC SPECIFICATIONS                                      | (RIN+, RIN-)                                                     |                                                     |                                               | ļ.                                |                                               |       |

| V <sub>TH</sub>     | Differential Threshold High<br>Voltage                       | (Figure 8)                                                       |                                                     |                                               | +90                               |                                               |       |

| V <sub>TL</sub>     | Differential Threshold Low<br>Voltage                        |                                                                  |                                                     | -90                                           |                                   |                                               | mV    |

| V <sub>IN</sub>     | Differential Input Voltage<br>Range                          | RIN+ - RIN-                                                      | 180                                                 |                                               |                                   | mV                                            |       |

| I <sub>IN</sub>     | Input Current                                                | $V_{IN} = V_{DD}$ or 0V,<br>$V_{DD} = 1.89V$                     |                                                     | -20                                           | ±1                                | +20                                           | μΑ    |

| R <sub>T</sub>      | Differential Internal<br>Termination Resistance              | Differential across RIN+ an                                      | d RIN-                                              | 80                                            | 100                               | 120                                           | Ω     |

| SER/DES             | SUPPLY CURRENT *DIGITAL                                      | , PLL, AND ANALOG VDD                                            | )                                                   | •                                             | •                                 | '                                             |       |

| I <sub>DDT</sub>    | Serializer (Tx) VDDn Supply Current (includes load current)  | $R_T = 100\Omega$<br>WORST CASE pattern<br>( <i>Figure 5</i> )   | VDDn = 1.89V<br>PCLK = 43 MHz<br>Default Registers  |                                               | 62                                | 90                                            | mA    |

|                     |                                                              | $R_T = 100\Omega$<br>RANDOM PRBS-7 pattern                       |                                                     |                                               | 55                                |                                               |       |

| I <sub>DDIOT</sub>  | Serializer (Tx) VDDIO Supply Current (includes load current) | $R_T = 100\Omega$<br>WORST CASE pattern<br>(Figure 5)            | VDDIO = 1.89V<br>PCLK = 43 MHz<br>Default Registers |                                               | 2                                 | 5                                             | w- A  |

|                     |                                                              |                                                                  | VDDIO = 3.6V<br>PCLK = 43 MHz<br>Default Registers  |                                               | 7                                 | 15                                            | mA    |

| I <sub>DDTZ</sub>   | Serializer (Tx) Supply Current                               |                                                                  | $V_{DDn} = 1.89V$                                   |                                               | 370                               | 775                                           |       |

| I <sub>DDIOTZ</sub> | Power-down                                                   | LVCMOS Inputs = 0V                                               | V <sub>DDIO</sub> = 1.89V                           |                                               | 55                                | 125                                           | μΑ    |

|                     |                                                              |                                                                  | V <sub>DDIO</sub> = 3.6V                            |                                               | 65                                | 135                                           |       |

| Symbol              | Parameter                                                            | Condition                                                                                 | ns                                                   | Min | Тур | Max | Units |

|---------------------|----------------------------------------------------------------------|-------------------------------------------------------------------------------------------|------------------------------------------------------|-----|-----|-----|-------|

| I <sub>DDR</sub>    | Deserializer (Rx) VDDn<br>Supply Current (includes load<br>current)  | $V_{DDn} = 1.89V$ $C_{L} = 8 \text{ pF}$ WORST CASE Pattern (Figure 5)                    | PCLK = 43 MHz<br>SSCG[3:0] = ON<br>Default Registers |     | 60  | 96  |       |

|                     |                                                                      | $V_{\rm DDn}$ = 1.89V<br>$C_{\rm L}$ = 8 pF<br>RANDOM PRBS-7 Pattern                      | PCLK = 43 MHz<br>Default Registers                   |     | 53  |     | mA    |

| I <sub>DDIOR</sub>  | Deserializer (Rx) VDDIO<br>Supply Current (includes load<br>current) | $V_{\rm DDIO}$ = 1.89V<br>$C_{\rm L}$ = 8 pF<br>WORST CASE Pattern<br>( <i>Figure 5</i> ) | PCLK = 43 MHz<br>Default Registers                   |     | 21  | 32  | IIIA  |

|                     |                                                                      | $V_{\rm DDIO}$ = 3.6V $C_{\rm L}$ = 8 pF WORST CASE Pattern                               | PCLK = 43 MHz<br>Default Registers                   |     | 49  | 83  |       |

| I <sub>DDRZ</sub>   | Deserializer (Rx) Supply                                             | PDB = 0V; All other                                                                       | V <sub>DDn</sub> = 1.89V                             |     | 42  | 400 |       |

| I <sub>DDIORZ</sub> | Current Power-down                                                   | LVCMOS Inputs = 0V                                                                        | V <sub>DDIO</sub> = 1.89V                            |     | 8   | 40  | μΑ    |

|                     |                                                                      |                                                                                           | $V_{DDIO} = 3.6V$                                    |     | 350 | 800 | 1     |

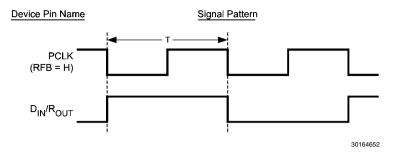

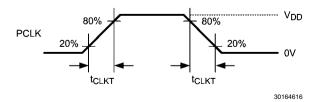

# Recommended Serializer Timing for PCLK (Note 12) Over recommended operating supply and temperature ranges unless otherwise specified.

| Symbol            | Parameter                             | Conditions      | Min  | Тур  | Max  | Units |

|-------------------|---------------------------------------|-----------------|------|------|------|-------|

| t <sub>TCP</sub>  | Transmit Clock Period                 | 10 MHz – 43 MHz | 23.3 | Т    | 100  | ns    |

| t <sub>TCIH</sub> | Transmit Clock Input High Time        |                 | 0.4T | 0.5T | 0.6T | ns    |

| t <sub>TCIL</sub> | Transmit Clock Input Low Time         |                 | 0.4T | 0.5T | 0.6T | ns    |

| t <sub>CLKT</sub> | PCLK Input Transition Time (Figure 9) |                 | 0.5  |      | 3    | ns    |

| f <sub>osc</sub>  | Internal oscillator clock source      |                 |      | 25   |      | MHz   |

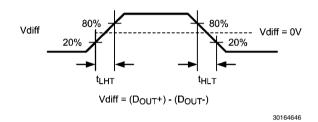

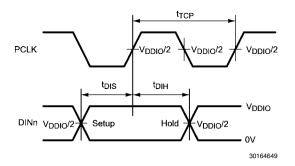

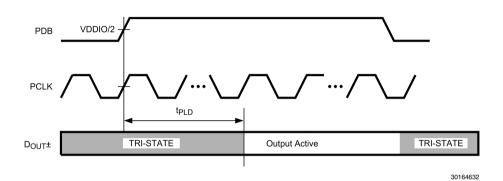

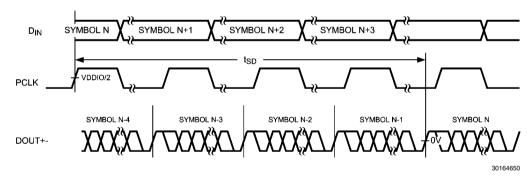

# Serializer Switching Characteristics Over recommended operating supply and temperature ranges unless otherwise specified.

| Symbol             | Parameter                                                     | Conditions                                                                                                                                                                                                      | Min           | Тур            | Max              | Units |

|--------------------|---------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|----------------|------------------|-------|

| t <sub>LHT</sub>   | CML Low-to-High Transition Time                               | $R_L = 100\Omega (Figure 6)$                                                                                                                                                                                    |               | 150            | 330              | ps    |

| t <sub>HLT</sub>   | CML High-to-Low<br>Transition Time                            | $R_L = 100\Omega (Figure 6)$                                                                                                                                                                                    |               | 150            | 330              | ps    |

| t <sub>DIS</sub>   | Data Input Setup to PCLK                                      | Serializer Data Inputs                                                                                                                                                                                          | 2.0           |                |                  | ns    |

| t <sub>DIH</sub>   | Data Input Hold from PCLK                                     | (Figure 10)                                                                                                                                                                                                     | 2.0           |                |                  | ns    |

| t <sub>PLD</sub>   | Serializer PLL Lock Time                                      | R <sub>L</sub> = 100Ω ( <i>Note 5</i> , <i>Note 11</i> )                                                                                                                                                        |               | 1              | 2                | ms    |

| t <sub>SD</sub>    | Serializer Delay                                              | $R_T = 100\Omega$<br>PCLK = 10–43 MHz<br>Register 0x03h b[0] (TRFB = 1)<br>( <i>Figure 12</i> )                                                                                                                 | 6.386T<br>+ 5 | 6.386T<br>+ 12 | 6.386T<br>+ 19.7 | ns    |

| t <sub>JIND</sub>  | Serializer Output<br>Deterministic Jitter                     | Serializer output intrinsic deterministic jitter . Measured (cycle-cycle) with PRBS-7 test pattern PCLK = 43 MHz (Note 4, Note 13)                                                                              |               | 0.13           |                  | UI    |

| t <sub>JINR</sub>  | Serializer Output Random<br>Jitter                            | Serializer output intrinsic random jitter (cycle-cycle). Alternating-1,0 pattern. PCLK = 43 MHz (Note 4, Note 13)                                                                                               |               | 0.04           |                  | UI    |

| t <sub>JINT</sub>  | Peak-to-peak Serializer<br>Output Jitter                      | Serializer output peak-to-peak jitter includes deterministic jitter, random jitter, and jitter transfer from serializer input. Measured (cycle-cycle) with PRBS-7 test pattern. PCLK = 43 MHz (Note 4, Note 13) |               | 0.396          |                  | UI    |

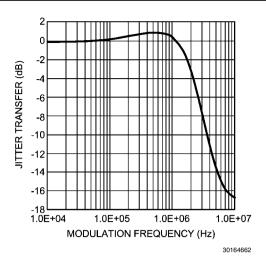

| λ <sub>STXBW</sub> | Serializer Jitter Transfer<br>Function -3 dB Bandwidth        | PCLK = 43 MHz Default Registers (Figure 18) (Note 4)                                                                                                                                                            |               | 1.90           |                  | MHz   |

| δ <sub>STX</sub>   | Serializer Jitter Transfer<br>Function (Peaking)              | PCLK = 43 MHz Default Registers (Figure 18) (Note 4)                                                                                                                                                            |               | 0.944          |                  | dB    |

| $\delta_{STXf}$    | Serializer Jitter Transfer<br>Function (Peaking<br>Frequency) | PCLK = 43 MHz Default Registers (Figure 18) (Note 4)                                                                                                                                                            |               | 500            |                  | kHz   |

# **Deserializer Switching Characteristics**Over recommended operating supply and temperature ranges unless otherwise specified.

| Symbol            | Parameter                                        | Conditions                                                                                          | Pin/Freq.                       | Min           | Тур                | Max            | Units |

|-------------------|--------------------------------------------------|-----------------------------------------------------------------------------------------------------|---------------------------------|---------------|--------------------|----------------|-------|

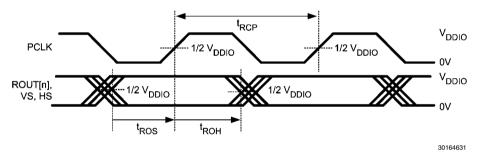

| t <sub>RCP</sub>  | Receiver Output Clock Period                     | $t_{RCP} = t_{TCP}$                                                                                 | PCLK                            | 23.3          | Т                  | 100            | ns    |

| t <sub>PDC</sub>  | PCLK Duty Cycle                                  | Default Registers<br>SSCG[3:0] = OFF                                                                | PCLK                            | 45            | 50                 | 55             | %     |

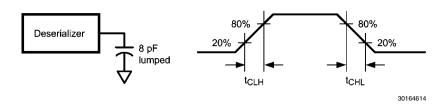

| t <sub>CLH</sub>  | LVCMOS Low-to-High Transition<br>Time            | V <sub>DDIO</sub> : 1.71V to 1.89V or 3.0 to 3.6V,                                                  | PCLK                            | 1.3           | 2.0                | 2.8            |       |

| t <sub>CHL</sub>  | LVCMOS High-to-Low Transition<br>Time            | C <sub>L</sub> = 8 pF (lumped load)<br>Default Registers<br>( <i>Figure 14</i> ) ( <i>Note 10</i> ) |                                 | 1.3           | 2.0                | 2.8            | ns    |

| t <sub>CLH</sub>  | LVCMOS Low-to-High Transition<br>Time            | V <sub>DDIO</sub> : 1.71V to 1.89V or 3.0 to 3.6V,                                                  | Deserializer ROUTn Data Outputs | 1.6           | 2.4                | 3.3            |       |

| t <sub>CHL</sub>  | LVCMOS High-to-Low Transition<br>Time            | C <sub>L</sub> = 8 pF (lumped load)<br>Default Registers<br>( <i>Figure 14</i> ) ( <i>Note 10</i> ) |                                 | 1.6           | 2.4                | 3.3            | ns    |

| t <sub>ROS</sub>  | ROUT Setup Data to PCLK                          | V <sub>DDIO</sub> : 1.71V to 1.89V or                                                               | Deserializer ROUTn              | 0.38T         | 0.5T               |                |       |

| t <sub>ROH</sub>  | ROUT Hold Data to PCLK                           | 3.0V to 3.6V,  C <sub>L</sub> = 8 pF (lumped load)  Default Registers                               | Data Outputs                    | 0.38T         | 0.5T               |                | ns    |

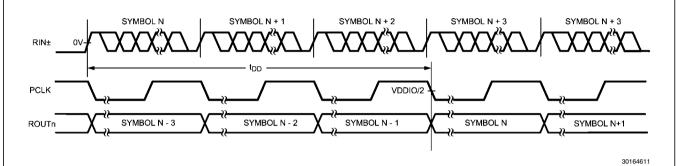

| t <sub>DD</sub>   | Deserializer Delay                               | Default Registers Register 0x03h b[0] (RRFB = 1) (Figure 15)                                        | 10 MHz-43 MHz                   | 4.571T<br>+ 8 | 4.571T<br>+ 12     | 4.571T<br>+ 16 | ns    |

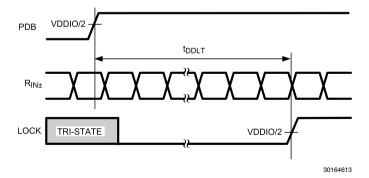

| t <sub>DDLT</sub> | Deserializer Data Lock Time                      | (Figure 13) (Note 5)                                                                                | 10 MHz-43 MHz                   |               |                    | 10             | ms    |

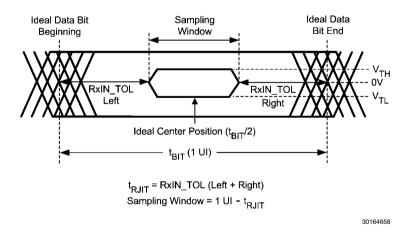

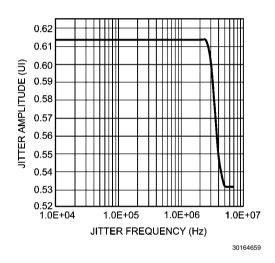

| t <sub>RJIT</sub> | Receiver Input Jitter Tolerance                  | (Figure 17, Figure 19)<br>(Note 13, Note 14)                                                        | 43 MHz                          |               | 0.53               |                | UI    |

| t <sub>RCJ</sub>  | Receiver Clock Jitter                            | PCLK                                                                                                | 10 MHz                          |               | 300                | 550            |       |

|                   |                                                  | SSCG[3:0] = OFF<br>( <i>Note 6</i> , <i>Note 10</i> )                                               | 43 MHz                          |               | 120                | 250            | ps    |

| t <sub>DPJ</sub>  | Deserializer Period Jitter                       | PCLK                                                                                                | 10 MHz                          |               | 425                | 600            |       |

|                   |                                                  | SSCG[3:0] = OFF<br>( <i>Note 7</i> , <i>Note 10</i> )                                               | 43 MHz                          |               | 320                | 480            | ps    |

| $t_{DCCJ}$        | Deserializer Cycle-to-Cycle Clock                |                                                                                                     | 10 MHz                          |               | 320                | 500            |       |

|                   | Jitter                                           | SSCG[3:0] = OFF<br>( <i>Note 8, Note 10</i> )                                                       | 43 MHz                          |               | 300                | 500            | ps    |

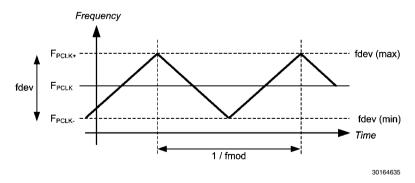

| fdev              | Spread Spectrum Clocking<br>Deviation Frequency  | LVCMOS Output Bus<br>SSC[3:0] = ON                                                                  | 20 MHz-43 MHz                   |               | ±0.5% to ±2.0%     |                | %     |

| fmod              | Spread Spectrum Clocking<br>Modulation Frequency | (Figure 20)                                                                                         | 20 MHz-43 MHz                   |               | 9 kHz to<br>66 kHz |                | kHz   |

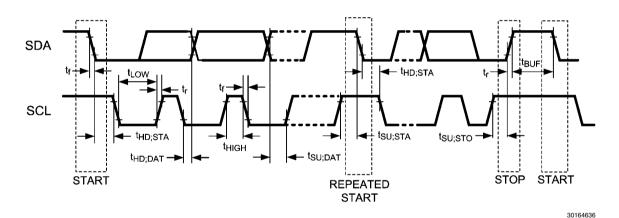

# Serial Control Bus AC Timing Specifications (SCL, SDA) - I<sup>2</sup>C Compliant (*Figure 4*)

Over recommended supply and temperature ranges unless otherwise specified.

| Symbol                                          | Parameter                                             | Conditions                 | Min | Тур | Max  | Units |  |  |  |

|-------------------------------------------------|-------------------------------------------------------|----------------------------|-----|-----|------|-------|--|--|--|

| RECOMMENDED INPUT TIMING REQUIREMENTS (Note 12) |                                                       |                            |     |     |      |       |  |  |  |

| f <sub>SCL</sub>                                | SCL Clock Frequency                                   |                            | >0  |     | 100  | kHz   |  |  |  |

| t <sub>LOW</sub>                                | SCL Low Period                                        | f <sub>SCL</sub> = 100 kHz | 4.7 |     |      | μs    |  |  |  |

| t <sub>HIGH</sub>                               | SCL High Period                                       |                            | 4.0 |     |      | μs    |  |  |  |

| t <sub>HD:STA</sub>                             | Hold time for a start or a repeated start condition   |                            | 4.0 |     |      | μs    |  |  |  |

| t <sub>SU:STA</sub>                             | Set Up time for a start or a repeated start condition |                            | 4.7 |     |      | μs    |  |  |  |

| t <sub>HD:DAT</sub>                             | Data Hold Time                                        |                            | 0   |     | 3.45 | μs    |  |  |  |

| t <sub>SU:DAT</sub>                             | Data Set Up Time                                      |                            | 250 |     |      | ns    |  |  |  |

| t <sub>SU:STO</sub>                             | Set Up Time for STOP Condition                        |                            | 4.0 |     |      | μs    |  |  |  |

| t <sub>r</sub>                                  | SCL & SDA Rise Time                                   |                            |     |     | 1000 | ns    |  |  |  |

| t <sub>f</sub>                                  | SCL & SDA Fall Time                                   |                            |     |     | 300  | ns    |  |  |  |

| C <sub>b</sub>                                  | Capacitive load for bus                               |                            |     |     | 400  | pF    |  |  |  |

| SWITCHII                                        | NG CHARACTERISTICS (Note 11)                          |                            |     |     |      |       |  |  |  |

| t <sub>HD:DAT</sub>                             | Data Hold Time                                        |                            | 0   |     | 3.45 | μs    |  |  |  |

| t <sub>SU:DAT</sub>                             | Data Set Up Time                                      |                            | 250 |     |      | ns    |  |  |  |

| t <sub>f</sub>                                  | SCL & SDA Fall Time                                   |                            |     |     | 300  | ns    |  |  |  |

FIGURE 4. Serial Control Bus Timing

### Serial Control Bus DC Characteristics (SCL, SDA) - I<sup>2</sup>C Compliant

Over recommended supply and temperature ranges unless otherwise specified.

| Symbol          | Parameter                | Conditions                                           | Min                        | Тур | Max                        | Units |

|-----------------|--------------------------|------------------------------------------------------|----------------------------|-----|----------------------------|-------|

| $V_{IH}$        | Input High Level         | SDA and SCL                                          | 0.7 x<br>V <sub>DDIO</sub> |     | V <sub>DDIO</sub>          | ٧     |

| $V_{IL}$        | Input Low Level Voltage  | SDA and SCL                                          | GND                        |     | 0.3 x<br>V <sub>DDIO</sub> | V     |

| V <sub>HY</sub> | Input Hysteresis         | SDA and SCL                                          |                            | >50 |                            | mV    |

| I <sub>OZ</sub> | TRI-STATE Output Current | PDB = 0V<br>V <sub>OUT</sub> = 0V or V <sub>DD</sub> | -20                        | ±1  | +20                        | μΑ    |

| I <sub>IN</sub> | Input Current            | SDA or SCL,<br>Vin = V <sub>DDIO</sub> or GND        | -20                        | ±1  | +20                        | μΑ    |

| Symbol          | Parameter                | Conditions                                           | Min | Тур | Max  | Units |

|-----------------|--------------------------|------------------------------------------------------|-----|-----|------|-------|

| C <sub>IN</sub> | Input Pin Capacitance    |                                                      |     | <5  |      | pF    |

| V <sub>OL</sub> | Low Level Output Voltage | SCL and SDA<br>$V_{DDIO} = 3.0V$<br>$I_{OL} = 1.5mA$ |     |     | 0.36 | V     |

|                 |                          | SCL and SDA<br>$V_{DDIO} = 1.71V$<br>$I_{OL} = 1mA$  |     |     | 0.36 | V     |

Note 1: "Absolute Maximum Ratings" indicate limits beyond which damage to the device may occur, including inoperability and degradation of device reliability and/or performance. Functional operation of the device and/or non-degradation at the Absolute Maximum Ratings or other conditions beyond those indicated in the Recommended Operating Conditions is not implied. The Recommended Operating Conditions at which the device is functional; the device should not be operated beyond such conditions.

Note 2: The Electrical Characteristics tables list guaranteed specifications under the listed Recommended Operating Conditions except as otherwise modified or specified by the Electrical Characteristics Conditions and/or Notes. Typical specifications are estimations only and are not guaranteed.

Note 3: Current into device pins is defined as positive. Current out of a device pin is defined as negative. Voltages are referenced to ground except VOD, ΔVOD, VTH and VTL which are differential voltages.

Note 4: Typical values represent most likely parametric norms at 1.8V or 3.3V, T<sub>A</sub> = +25°C, and at the Recommended Operation Conditions at the time of product characterization and are not guaranteed.

Note 5: t<sub>PLD</sub> and t<sub>DDLT</sub> is the time required by the serializer and deserializer to obtain lock when exiting power-down state with an active PCLK

Note 6: t<sub>DCL</sub> is the maximum amount of jitter measured over 30,000 samples based on Time Interval Error (TIE).

Note 7: t<sub>DPJ</sub> is the maximum amount the period is allowed to deviate measured over 30,000 samples.

Note 8: t<sub>DCC.I</sub> is the maximum amount of jitter between adjacent clock cycles measured over 30,000 samples.

Note 9: Supply noise testing was done with minimum capacitors (as shown on Figures 27, 28) on the PCB. A sinusoidal signal is AC coupled to the VDDn (1.8V) supply with amplitude = 25 mVp-p measured at the device VDDn pins. Bit error rate testing of input to the Ser and output of the Des with 10 meter cable shows no error when the noise frequency on the Ser is less than 1 MHz. The Des on the other hand shows no error when the noise frequency is less than 750 kHz.

Note 10: Specification is guaranteed by characterization and is not tested in production.

Note 11: Specification is guaranteed by design.

Note 12: Recommended Input Timing Requirements are input specifications and not tested in production.

Note 13: UI - Unit Interval is equivalent to one ideal serialized data bit width. The UI scales with PCLK frequency.

Note 14:  $t_{RJIT}$  max (0.61UI) is limited by instrumentation and actual  $t_{RJIT}$  of in-band jitter at low frequency (<2 MHz) is greater 1 UI.

### **AC Timing Diagrams and Test Circuits**

FIGURE 5. "Worst Case" Test Pattern

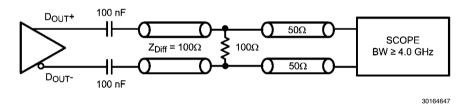

FIGURE 6. Serializer CML Output Load and Transition Times

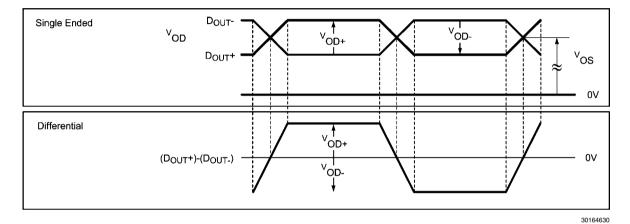

FIGURE 7. Serializer VOD DC Diagram

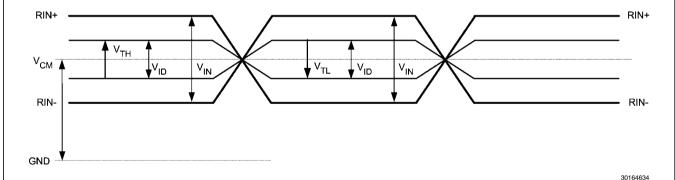

FIGURE 8. Differential VTH/VTL Definition Diagram

FIGURE 9. Serializer Input Clock Transition Times

FIGURE 10. Serializer Setup/Hold Times

FIGURE 11. Serializer Data Lock Time

FIGURE 12. Serializer Delay

FIGURE 13. Deserializer Data Lock Time

FIGURE 14. Deserializer LVCMOS Output Load and Transition Times

FIGURE 15. Deserializer Delay

FIGURE 16. Deserializer Output Setup/Hold Times

FIGURE 17. Receiver Input Jitter Tolerance

FIGURE 18. Typical Serializer Jitter Transfer Function Curve at 43 MHz

FIGURE 19. Typical Deserializer Input Jitter Tolerance Curve at 43 MHz

FIGURE 20. Spread Spectrum Clock Output Profile

### **TABLE 1. DS90UR903Q Control Registers**

| Addr<br>(Hex) | Name                       | Bits     | Field                | R/W | Default                                                                                                                                | Description                                                                                                       |  |

|---------------|----------------------------|----------|----------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|--|

| 0             | I <sup>2</sup> C Device ID | 7:1<br>0 | DEVICE ID SER ID SEL | RW  | 0xB0'h                                                                                                                                 | 7-bit address of Serializer; 0x58'h<br>(1011_000X'b) default<br>0: Device ID is from ID[x]                        |  |

|               |                            | Ů        | OEITID OEE           |     |                                                                                                                                        | 1: Register I <sup>2</sup> C Device ID overrides ID[x]                                                            |  |

|               |                            | 7:3      | RESERVED             |     | 0x00'h                                                                                                                                 | Reserved                                                                                                          |  |

|               |                            | 2        | RESERVED             | RW  | 0                                                                                                                                      | Reserved                                                                                                          |  |

| 1             | Reset                      | 1        | DIGITAL<br>RESET0    | RW  | 0<br>self clear                                                                                                                        | 1: Resets the device to default register values. Does not affect device I <sup>2</sup> C Bus or Device ID         |  |

|               |                            | 0        | DIGITAL RESET1       | RW  | 0<br>self clear                                                                                                                        | 1: Digital Reset, retains all register values                                                                     |  |

| 2             | Reserved                   | 7:0      | RESERVED             |     | 0x20'h                                                                                                                                 | Reserved                                                                                                          |  |

|               | Reserved                   | 7:6      | RESERVED             |     | 11'b                                                                                                                                   | Reserved                                                                                                          |  |

|               | VDDIO Control              | 5        | VDDIO CONTOL         | RW  | 1                                                                                                                                      | Auto V <sub>DDIO</sub> detect Allows manual setting of VDDIO by register. 0: Disable 1: Enable (auto detect mode) |  |

|               | VDDIO Mode                 | 4        | VDDIO MODE           | RW  | 1                                                                                                                                      | VDDIO voltage set Only used when VDDIOCONTROL = 0 0: 1.8V 1: 3.3V                                                 |  |

| 3             | RESERVED                   | 3        | RESERVED             | RW  | 1                                                                                                                                      | Reserved                                                                                                          |  |

| 3             | RESERVED                   | 2        | RESERVED             |     | 0                                                                                                                                      | Reserved                                                                                                          |  |

|               | PCLK_AUTO                  | 1        | PCLK_AUTO            | RW  | 1                                                                                                                                      | Switch over to internal 25 MHz Oscillator clock in the absence of PCLK 0: Disable 1: Enable                       |  |

|               | TRFB                       | 0        | TRFB                 | RW  | Pixel Clock Edge Select: 0: Parallel Interface Data is strobed on the Fa 1 Edge. 1: Parallel Interface Data is strobed on the Ri Edge. |                                                                                                                   |  |

| 4             | Reserved                   | 7:0      | RESERVED             |     | 0x80'h                                                                                                                                 | Reserved                                                                                                          |  |

| 5             | Reserved                   | 7:0      | RESERVED             | RW  | 0x40'h                                                                                                                                 | Reserved                                                                                                          |  |

| 6             | Reserved                   | 7:0      | RESERVED             | RW  | 0xC0'h                                                                                                                                 | Reserved                                                                                                          |  |

| 7             | Reserved                   | 7:0      | RESERVED             | RW  | 0x00'h                                                                                                                                 | Reserved                                                                                                          |  |

| 8             | Reserved                   | 7:0      | RESERVED             |     | 0x00'h                                                                                                                                 | Reserved                                                                                                          |  |

| 9             | Reserved                   | 7:0      | RESERVED             |     | 0x01'h                                                                                                                                 | Reserved                                                                                                          |  |

| Α             | Reserved                   | 7:0      | RESERVED             |     | 0x00'h                                                                                                                                 | Reserved                                                                                                          |  |

| В             | Reserved                   | 7:0      | RESERVED             |     | 0x00'h                                                                                                                                 | Reserved                                                                                                          |  |

|               | Reserved                   | 7:3      | RESERVED             |     | 0x00'h                                                                                                                                 | Reserved                                                                                                          |  |

| С             | PCLK Detect                | 2        | PCLK DETECT          | R   | 0                                                                                                                                      | 1: Valid PCLK detected 0: Valid PCLK not detected                                                                 |  |

|               | Reserved                   | 3        | RESERVED             |     | 0                                                                                                                                      | Reserved                                                                                                          |  |

|               | Reserved                   | 0        | RESERVED             | R   | 0                                                                                                                                      | Reserved                                                                                                          |  |

| D             | Reserved                   | 7:0      | RESERVED             |     | 0x11'h                                                                                                                                 | Reserved                                                                                                          |  |

| Е             | Reserved                   | 7:0      | RESERVED             |     | 0x01'h                                                                                                                                 | Reserved                                                                                                          |  |

| F             | Reserved                   | 7:0      | RESERVED             |     | 0x03'h                                                                                                                                 | Reserved                                                                                                          |  |

| 10            | Reserved                   | 7:0      | RESERVED             |     | 0x03'h                                                                                                                                 | Reserved                                                                                                          |  |

| 11            | Reserved                   | 7:0      | RESERVED             |     | 0x03'h                                                                                                                                 | Reserved                                                                                                          |  |

| Addr<br>(Hex) | Name                           | Bits | Field                                                                                | R/W | Default | Description       |

|---------------|--------------------------------|------|--------------------------------------------------------------------------------------|-----|---------|-------------------|

| 12            | Reserved                       | 7:0  | RESERVED                                                                             |     | 0x03'h  | Reserved          |

| 13            | General Purpose<br>Control Reg | 7:0  | GPCR[7]<br>GPCR[6]<br>GPCR[5]<br>GPCR[4]<br>GPCR[3]<br>GPCR[2]<br>GPCR[1]<br>GPCR[0] | RW  | 0x00'h  | 0: LOW<br>1: HIGH |

### **TABLE 2. DS90UR904Q Control Registers**

| Addr<br>(Hex) | Name                       | Bits | Field            | R/W | Default         | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|---------------|----------------------------|------|------------------|-----|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0             | I <sup>2</sup> C Device ID | 7:1  | DEVICE ID        | RW  | 0xC0'h          | 7-bit address of Deserializer;<br>0x60h<br>(1100_000X) default                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|               |                            | 0    | DES ID SEL       |     |                 | 0: Device ID is from ID[x] 1: Register I <sup>2</sup> C Device ID overrides ID[x]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|               |                            | 7:3  | RESERVED         |     | 0x00'h          | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |