# Fairchild Semiconductors

## **Semiconductors**Integrated Circuits – TTL Monostables

### 9600 Series Monostables

### REFERENCE TABLE

| Code             | Function                | Pulse W<br>Variation<br>V <sub>s</sub> Temp |      | Number<br>Inputs<br>Positive | of<br>Negative | Reset- | Min.<br>Output<br>tpw<br>ns | Power<br>Dissi-<br>pation<br>mW | Stock<br>No.     |

|------------------|-------------------------|---------------------------------------------|------|------------------------------|----------------|--------|-----------------------------|---------------------------------|------------------|

| 9600DM<br>9600PC | Single<br>Retriggerable | ±1.5                                        | ±1.5 | 3                            | 2              | ١      | 75                          | 125                             | 35782G<br>35783E |

| 9601DC<br>9601PC | Single<br>Retriggerable | ±2.7                                        | ±1.0 | 2                            | 2              |        | 50                          | 125                             | 35784C<br>35785A |

| 9602DC<br>9602PC | Dual<br>Retriggerable   | ±1.5                                        | ±1.5 | 1                            | 1              | ``     | 72                          | 250                             | 35786X<br>35787H |

#### **GENERAL DESCRIPTION**

The 9600 series monostable multivibrators provide an output pulse whose duration and accuracy is a function of the external timing components. The 9600 series have excellent immunity to noise on the  $V_{\text{CC}}$  and ground lines. The 9600 series uses TTL for high speed and high fan out capability and is compatible with all members of the Fairchild TTL family.

### 9600 RETRIGGERABLE RESETTABLE MONOSTABLE

### **FUNCTIONAL DESCRIPTION**

The 9600 monostable multivibrator has five inputs, three active HIGH and two active LOW. This allows leading edge or trailing edge triggering. The TTL inputs make triggering independent of input transition times. When input conditions for triggering are met, a new cycle starts and the external capacitor is rapidly discharged and then allowed to charge. An input cycle time shorter than the output cycle time will retrigger the 9600 and result in a continuous true output. Retriggering may be inhibited by tying the negation (Q) output to an active LOW input. The output pulse may be terminated at any time by connecting either or both reset pins to a LOW logic level pin. Active pullups are provided on the outputs for good drive capability into capacitive loads.

### **FEATURES**

74ns to ∞ output pulse width range.

Retriggerable 0 to 100% duty cycle.

Resettable.

TTL input gating - leading or trailing edge triggering.

Complementary TTL outputs.

Optional retrigger lock-out capability.

Improved pulse width temperature stability.

### **ABSOLUTE MAXIMUM RATINGS**

| Storage temperature                              | -65°C to +150°C           |  |  |  |

|--------------------------------------------------|---------------------------|--|--|--|

| Temperature (ambient) under bias                 | 55°C to +125°C            |  |  |  |

| V <sub>CC</sub> pin potential to ground          | -0.5V to +8.0V            |  |  |  |

| Input voltage (DC)                               | -0.5V to +5.5V            |  |  |  |

| Input current                                    | -30mA to +5.0mA           |  |  |  |

| Voltage applied to output<br>when output is HIGH | -0.5V to +V <sub>cc</sub> |  |  |  |

| Current into output when output is LOW           | 50mA                      |  |  |  |

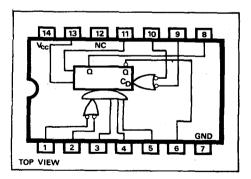

### CONNECTION DIAGRAM

See outline drawing Nos. 130 and 151 for dimensions.

Continued on next page