# Resonant Fluorescent Lamp Driver

#### **FEATURES**

- 1µA ICC when Disabled

- PWM Control for LCD Supply

- Zero Voltage Switched (ZVS) on Push-Pull Drivers

- Open Lamp Detect Circuitry

- 4.5V to 20V Operation

- Non-saturating Transformer Topology

- Smooth 100% Duty Cycle on Buck PWM and 0% to 95% on Flyback PWM

#### DESCRIPTION

The UC1871 Family of IC's is optimized for highly efficient fluorescent lamp control. An additional PWM controller is integrated on the IC for applications requiring an additional supply, as in LCD displays. When disabled the IC draws only  $1\mu A$ , providing a true disconnect feature, which is optimum for battery powered systems. The switching frequency of all outputs are synchronized to the resonant frequency of the external passive network, which provides Zero Voltage Switching on the Push-Pull drivers.

Soft-Start and open lamp detect circuitry have been incorporated to minimize component stress. An open lamp is detected on the completion of a soft-start cycle.

The Buck controller is optimized for smooth duty cycle control to 100%, while the flyback control ensures a maximum duty cycle of 95%.

Other features include a precision 1% reference, under voltage lockout, flyback current limit, and accurate minimum and maximum frequency control.

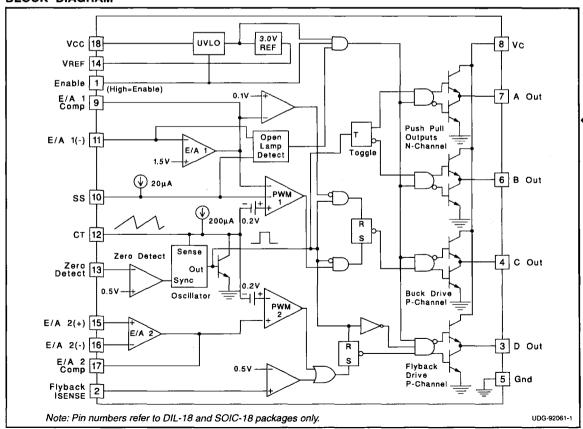

#### **BLOCK DIAGRAM**

PIN

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

## **ABSOLUTE MAXIMUM RATINGS** Analog Inputs . . . . . . . . . . . . . . . . . . -0.3 to +10V Zero Detect Input Current High Impedance Source . . . . . . . . +10mA Zero Detect Low Impedance Source. . . . . . . . . . +20V Storage Temperature . . . . . . . . -65°C to +150°C

Note 1: Currents are positive into, negative out of the specified ter-

Note 2: Consult Packaging Section of Databook for thermal limitations and considerations of package.

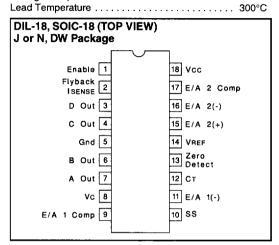

#### CONNECTION DIAGRAMS

ELECTRICAL CHARACTERISTICS Unless otherwise stated, these parameters apply for TA = -55°C to +125°C for the UC1871; -25°C to +85°C for the UC2871; 0°C to +70°C for the UC3871; Vcc = 5V, Vc = 15V, VENABLE = 5V, CT = 1nF, Zero Det = 1V.

| PARAMETER                | TEST CONDITIONS                | MIN         | TYP   | MAX    | UNITS |

|--------------------------|--------------------------------|-------------|-------|--------|-------|

| Reference Section        |                                | <del></del> |       |        |       |

| Output Voltage           | TJ=25°C                        | 2.963       | 3.000 | 3.037  | V     |

|                          | Overtemp                       | 2.940       | 3.000 | 3.060  | V     |

| Line Regulation          | Vcc = 4.75V to 18V             |             |       | 10     | mV    |

| Load Regulation          | lo=0 to -5mA                   |             |       | 10     | mV    |

| Oscillator Section       |                                |             |       |        |       |

| Free Running Freq        | TJ=25°C                        | 57          | 68    | 78     | kHz   |

| Max Sync Frequency       | TJ=25°C                        | 160         | 200   | 240    | kHz   |

| Charge Current           | VCT = 1.5V                     | 180         | 200   | 220    | μА    |

| Voltage Stability        |                                |             |       | 2      | %     |

| Temperature Stability    |                                |             | 4     | 8      | %     |

| Zero Detect Threshold    |                                | 0.46        | 0.5   | 0.56   | ٧     |

| Error Amp 1 Section      |                                |             |       |        |       |

| Input Voltage            | Vo = 2V                        | 1.445       | 1.475 | 1.505  | ٧     |

| Input Bias Current       |                                |             | -0.4  | -2     | μΑ    |

| Open Loop Gain           | Vo = 0.5 to 3V                 | 65          | 90    |        | dB    |

| Output High              | VEA(-) = 1.3V                  | 3.1         | 3.5   | 3.9    | V     |

| Output Low               | VEA(-) = 1.7V                  |             | 0.1   | 0.2    | V     |

| Output Source Current    | VEA(-) = 1.3V, Vo = 2V         | -350        | -500  |        | μА    |

| Output Sink Current      | VEA(-) = 1.7V, Vo = 2V         | 10          | 20    |        | mA    |

| Common Mode Range        |                                | 0           |       | VIN-1V | V     |

| Unity Gain Bandwidth     | T <sub>J</sub> = 25°C (Note 4) |             | 1     |        | MHz   |

| Maximum Source Impedance | Note 5                         |             |       | 100k   | Ω     |

# ELECTRICAL CHARACTERISTICS (cont.)

Unless otherwise stated, these parameters apply for TA = -55°C to +125°C for the UC1871; -25°C to +85°C for the UC2871; 0°C to +70°C for the UC3871; Vcc = 5V, Vc = 15V, VENABLE = 5V, CT = 1nF, Zero Det = 1V.

| PARAMETER                     | TEST CONDITIONS                         | MIN      | TYP   | MAX    | UNITS |

|-------------------------------|-----------------------------------------|----------|-------|--------|-------|

| Open Lamp Detect Section      |                                         |          |       | _      |       |

| Soft Start Threshold          | VEA(-) = 0V                             | 2.9      | 3.4   | 3.8    | V     |

| Error Amp Threshold           | Vss = 4.2V                              | 0.7      | 1.0   | 1.3    | V     |

| Soft Start Current            | Vss = 2V                                | 10       | 20    | 40     | μА    |

| Error Amp 2 Section           |                                         | <u> </u> |       | ·      |       |

| Input Offset Voltage          | Vo = 2V                                 |          | 0     | 10     | mV    |

| Input Bias Current            |                                         |          | -0.2  | -1     | μА    |

| Input Offset Current          |                                         |          |       | 0.5    | μА    |

| Open Loop Gain                | Vo = 0.5 to 3V                          | 65       | 90    |        | dB    |

| Output High                   | VID = 100mV, Vo = 2V                    | 3.6      | 4     | 4.4    | V     |

| Output Low                    | VID = -100mv, Vo = 2V                   |          | 0.1   | 0.2    | V     |

| Output Source Current         | VID = 100mV, Vo = 2V                    | -350     | -500  | ļ ——   | μА    |

| Output Sink Current           | VID = -100mV, Vo = 2V                   | 10       | 20    |        | mA    |

| Common Mode Range             |                                         | 0        |       | VIN-2V | V     |

| Unity Gain Bandwidth          | T <sub>J</sub> = 25°C (Note 4)          |          | 1     |        | MHz   |

| Isense Section                |                                         |          |       |        |       |

| Threshold                     |                                         | 0.475    | 0.525 | 0.575  | V     |

| Output Section                |                                         |          | •     |        |       |

| Output Low Level              | IOUT = 0, Outputs A and B               |          | 0.05  | 0.2    | V     |

| ·                             | IOUT = 10mA                             |          | 0.1   | 0.4    | V     |

|                               | IOUT = 100mA                            |          | 1.5   | 2.2    | V     |

| Output High Level             | IOUT = 0, Outputs C and D               | 14.7     | 14.9  |        | V     |

|                               | IOUT = -10mA                            | 13.5     | 14.3  |        | V     |

|                               | IOUT = -100mA                           | 12.5     | 13.5  |        | V     |

| Rise Time                     | T <sub>J</sub> = 25°C, Cl = 1nF(Note 4) |          | 30    | 80     | ns    |

| Fall Time                     | T <sub>J</sub> = 25°C, Cl = 1nF(Note 4) |          | 30    | 80     | ns    |

| Output Dynamics               |                                         |          |       | _      |       |

| Out A and B Duty Cycle        |                                         | 48       | 49.9  | 50     | %     |

| Out C Max Duty Cycle          | VEA1(-) = 1V                            | 100      |       |        | %     |

| Out C Min Duty Cycle          | VEA1(-) = 2V                            |          |       | 0      | %     |

| Out D Max Duty Cycle          | VEA2(+)- VEA2(-) = 100mV                |          | 92    | 96     | %     |

| Out D Min Duty Cycle          | VEA2(+)- VEA2(-) = -100mV               |          |       | 0      | %     |

| Under Voltage Lockout Section |                                         |          | •     |        |       |

| Start-Up Threshold            |                                         | 3.7      | 4.2   | 4.5    | V     |

| Hysterisis                    |                                         | 120      | 200   | 280    | m∨    |

| Enable Section                |                                         |          |       |        |       |

| Input High Threshold          |                                         | 2        |       |        | ٧     |

| Input low Threshold           |                                         |          |       | 0.8    | ٧     |

| Input Current                 | VENABLE = 5V                            |          | 150   | 400    | μΑ    |

| Supply Current Section        |                                         |          |       |        |       |

| VCC Supply Current            | Vcc = 20V                               |          | 8     | 14     | mA    |

| VC Supply Current             | Vc=20V                                  |          | 7     | 12     | mA    |

| ICC Disabled                  | VCC = 20V, VENABLE = 0V                 | Î        | 1     | 10     | μА    |

|                               |                                         |          |       |        |       |

Note 3: Unless otherwise specified, all voltages are with respect to ground. Currents are positive into, and negative out of the specified terminal.

Note 4: Guaranteed by design but not 100% tested in production.

Note 5: Impedance below specified maximum guarantees proper operation of the Open Lamp Detect.

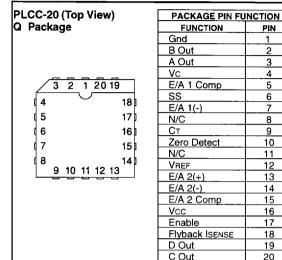

Figure 1

#### **APPLICATION INFORMATION**

Figure 1 shows a complete application circuit using the UC3871 Resonant Fluorescent lamp and LCD driver. The IC provides all drive, control and housekeeping functions to implement CCFL and LCD converters. The buck output voltage (transformer center-tap) provides the zero crossing and synchronization signal. The LCD supply modulator is also synchronized to the resonant tank.

The buck modulator drives a P-channel MOSFET directly, and operates over a 0-100% duty-cycle range. The modulation range includes 100%, allowing operation with minimal headroom. The LCD supply modulator also directly drives a P-channel MOSFET, but it's duty-cycle is limited to 95% to prevent flyback supply foldback.

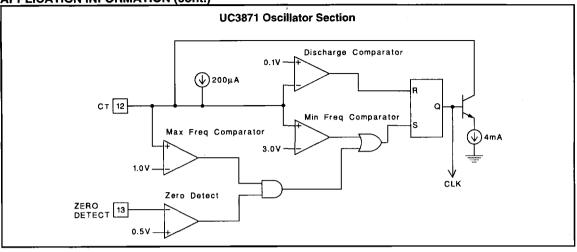

The oscillator and synchronization circuitry are shown in Figure 2. The oscillator is designed to synchronize over a 3:1 frequency range. In an actual application however, the frequency range is only about 1.5:1. A zero detect

comparator senses the primary center-tap voltage, generating a synchronization pulse when the resonant waveform falls to zero. The actual threshold is 0.5 volts, providing a small amount of anticipation to offset propagation delay.

The synchronization pulse width is the time that the 4mA current sink takes to discharge the timing capacitor to 0.1 volts. This pulse width sets the LCD supply modulator minimum off time, and also limits the minimum linear control range of the buck modulator. The  $200\mu A$  current source charges the capacitor to a maximum of 3 volts. A comparator blanks the zero detect signal until the capacitor voltage exceeds 1 volt, preventing multiple synchronization pulse generation and setting the maximum frequency. If the capacitor voltage reaches 3 volts (a zero detection has not occurred) an internal clock pulse is generated to limit the minimum frequency.

## **APPLICATION INFORMATION (cont.)**

Figure 2

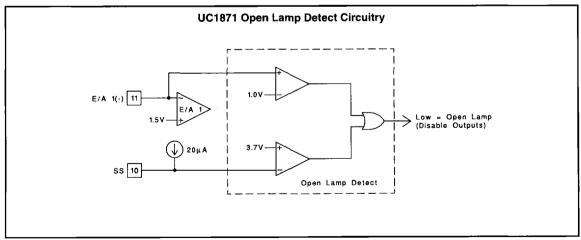

A unique protection feature incorporated in the UC3871 is the Open Lamp Detect circuit. An open lamp interrupts the current feedback loop and causes very high secondary voltage. Operation in this mode will usually breakdown the transformer's insulation, causing permanent damage to the converter. The open lamp detect circuit, shown in Figure 3 senses the lamp current feedback signal at the error amplifiers input, and shuts down the outputs if insufficient signal is present. Soft-start circuitry limits initial turn-on currents and blanks the open lamp detect signal.

Other features are included to minimize external circuitry

requirements. A logic level enable pin shuts down the IC, allowing direct connection to the battery. During shutdown, the IC typically draws less than 1μA. The UC3871, operating from 4.5V to 20V, is compatible with almost all battery voltages used in portable computers. Under-voltage lockout circuitry disables operation until sufficient supply voltage is available, and a 1% voltage reference insures accurate operation. Both inputs to the LCD supply error amplifier are uncommitted, allowing positive or negative supply loop closure without additional circuitry. The LCD supply modulator also incorporates cycle-bycycle current limiting for added protection.

Figure 3

UNITRODE CORPORATION

7 CONTINENTAL BLVD. • MERRIMACK, NH 03054

TEL. (603) 424-2410 • FAX (603) 424-3460