# 1:6 LOW JITTER UNIVERSAL BUFFER/LEVEL TRANSLATOR WITH 2:1 INPUT MUX AND INDIVIDUAL OE (<1.25 GHz)

#### **Features**

- 6 differential or 12 LVCMOS outputs Independent V<sub>DD</sub> and V<sub>DDO</sub>:

- Ultra-low additive jitter: 45 fs rms

- Wide frequency range: dc to 1.25 GHz

- Universal input with pin selectable output formats

- LVPECL, Low Power LVPECL, LVDS, CML, HCSL, LVCMOS

- 2:1 mux with hot-swappable inputs

- Individual output enable

- Independent V<sub>DD</sub> and V<sub>DDO</sub>: 1.8/2.5/3.3 V

- 1.2/1.5 V LVCMOS output support

- Excellent power supply noise rejection (PSRR)

- Selectable LVCMOS drive strength to tailor jitter and EMI performance

- Small size: 32-QFN (5x5 mm)

- RoHS compliant, Pb-free

- Industrial temperature range: -40 to +85 °C

#### **Applications**

- High-speed clock distribution

- Ethernet switch/router

- Optical Transport Network (OTN)

- SONET/SDH

- PCI Express Gen 1/2/3

- Storage

- Telecom

- Industrial

- Servers

- Backplane clock distribution

# **Description**

The Si53314 is an ultra low jitter six output differential buffer with pin-selectable output clock signal format and individual OE. The Si53314 features a 2:1 mux making it ideal for redundant clocking applications. The Si53314 utilizes Skyworks Solutions' advanced CMOS technology to fanout clocks from dc to 1.25 GHz with guaranteed low additive jitter, low skew, and low propagation delay variability. The Si53314 features minimal cross-talk and provides superior supply noise rejection, simplifying low jitter clock distribution in noisy environments. Independent core and output bank supply pins provide integrated level translation without the need for external circuitry.

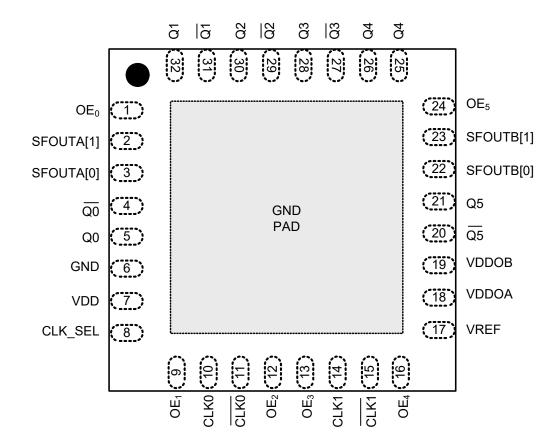

#### Pin Assignments Si53314 8 8 81 8 81 8 81 8 (24) OE<sub>5</sub> OE<sub>0</sub> Œ (23) SFOUTB[1] SFOUTA[1] (22) SFOUTB[0] SFOUTA[0] (3) (21) <u>q</u> (4) 20 <u>05</u> Q0 (5) GND (6) VDDOB (19) (18) VDDOA VDD (7) (17) VREF CLK\_SEL CLK GE GE CLK GE GE CLK GE GE CLK GE

Patents pending

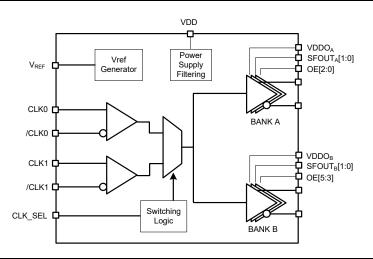

#### **Functional Block Diagram**

# Si53314

# TABLE OF CONTENTS

| Section                                                    | Page |

|------------------------------------------------------------|------|

| 1. Electrical Specifications                               |      |

| 2. Functional Description                                  |      |

| 2.1. Universal, Any-Format Input                           |      |

| 2.2. Input Bias Resistors                                  |      |

| 2.3. Input Clock Voltage Reference (VREF)                  |      |

| 2.4. Universal, Any-Format Output Buffer                   |      |

| 2.5. Input Mux and Output Enable Logic                     |      |

| 2.6. Power Supply (V <sub>DD</sub> and V <sub>DDOX</sub> ) |      |

| 2.7. Output Clock Termination Options                      | 16   |

| 2.8. AC Timing Waveforms                                   |      |

| 2.9. Typical Phase Noise Performance                       | 20   |

| 2.10. Input Mux Noise Isolation                            |      |

| 2.11. Power Supply Noise Rejection                         |      |

| 3. Pin Descriptions                                        | 24   |

| 4. Ordering Guide                                          |      |

| 5. Package Outline                                         | 28   |

| 5.1. 5x5 mm 32-QFN Package Diagram                         | 28   |

| 6. PCB Land Pattern                                        | 29   |

| 6.1. 5x5 mm 32-QFN Package Land Pattern                    | 29   |

| 7. Top Marking                                             |      |

| 7.1. Si53314 Top Marking                                   |      |

| 7.2. Top Marking Explanation                               |      |

| Document Change List                                       |      |

| Contact Information                                        |      |

# 1. Electrical Specifications

**Table 1. Recommended Operating Conditions**

| Parameter                        | Symbol            | Test Condition                      | Min  | Тур | Max  | Unit |

|----------------------------------|-------------------|-------------------------------------|------|-----|------|------|

| Ambient Operating<br>Temperature | T <sub>A</sub>    |                                     | -40  | _   | 85   | °C   |

| Supply Voltage Range*            | V <sub>DD</sub>   | LVDS, CML                           | 1.71 | 1.8 | 1.89 | V    |

|                                  |                   |                                     | 2.38 | 2.5 | 2.63 | V    |

|                                  |                   |                                     | 2.97 | 3.3 | 3.63 | V    |

|                                  |                   | LVPECL, low power LVPECL,<br>LVCMOS | 2.38 | 2.5 | 2.63 | V    |

|                                  |                   |                                     | 2.97 | 3.3 | 3.63 | V    |

|                                  |                   | HCSL                                | 2.97 | 3.3 | 3.63 | V    |

| Output Buffer Supply             | V <sub>DDOX</sub> | LVDS, CML, LVCMOS                   | 1.71 | 1.8 | 1.89 | V    |

| Voltage*                         |                   |                                     | 2.38 | 2.5 | 2.63 | V    |

|                                  |                   |                                     | 2.97 | 3.3 | 3.63 | V    |

|                                  |                   | LVPECL, low power LVPECL            | 2.38 | 2.5 | 2.63 | V    |

|                                  |                   |                                     | 2.97 | 3.3 | 3.63 | V    |

|                                  |                   | HCSL                                | 2.97 | 3.3 | 3.63 | V    |

\*Note: Core supply V<sub>DD</sub> and output buffer supplies V<sub>DDO</sub> are independent. LVCMOS clock input is not supported for V<sub>DD</sub> = 1.8V but is supported for LVCMOS clock output for V<sub>DDOX</sub> = 1.8V. LVCMOS outputs at 1.5V and 1.2V can be supported via a simple resistor divider network. See "2.7.1. LVCMOS Output Termination To Support 1.5 and 1.2 V"

**Table 2. Input Clock Specifications**

(V<sub>DD</sub>=1.8 V  $\pm$  5%, 2.5 V  $\pm$  5%, or 3.3 V  $\pm$  10%, T<sub>A</sub>=–40 to 85 °C)

| Parameter                                 | Symbol          | Test Condition                                           | Min                   | Тур | Max                      | Unit   |

|-------------------------------------------|-----------------|----------------------------------------------------------|-----------------------|-----|--------------------------|--------|

| Differential Input Common<br>Mode Voltage | V <sub>CM</sub> | $V_{DD} = 2.5 \text{ V} \pm 5\%, 3.3 \text{ V} \pm 10\%$ | 0.05                  | _   |                          | V      |

| Differential Input Swing (peak-to-peak)   | V <sub>IN</sub> |                                                          | 0.2                   |     | 2.2                      | ٧      |

| LVCMOS Input High Voltage                 | V <sub>IH</sub> | $V_{DD} = 2.5 V \pm 5\%, 3.3 V \pm 10\%$                 | V <sub>DD</sub> x 0.7 | _   |                          | \<br>\ |

| LVCMOS Input Low Voltage                  | V <sub>IL</sub> | $V_{DD} = 2.5 \text{ V} \pm 5\%, 3.3 \text{ V} \pm 10\%$ | _                     | _   | V <sub>DD</sub> x<br>0.3 | \<br>\ |

| Input Capacitance                         | C <sub>IN</sub> | CLK0 and CLK1 pins with respect to GND                   | _                     | 5   | _                        | pF     |

**Table 3. DC Common Characteristics**

(V<sub>DD</sub> = 1.8 V  $\pm$  5%, 2.5 V  $\pm$  5%, or 3.3 V  $\pm$  10%,  $T_A$  = –40 to 85 °C)

| Parameter                            | Symbol            | Test Condition                                                              | Min           | Тур           | Max           | Unit |

|--------------------------------------|-------------------|-----------------------------------------------------------------------------|---------------|---------------|---------------|------|

| Supply Current                       | I <sub>DD</sub>   |                                                                             | _             | 65            | 100           | mA   |

| Output Buffer                        | I <sub>DDOX</sub> | LVPECL (3.3 V)                                                              | _             | 35            | _             | mA   |

| Supply Current<br>(Per Clock Output) |                   | Low Power LVPECL (3.3 V)*                                                   | _             | 35            | _             | mA   |

| @100 MHz (diff)                      |                   | LVDS (3.3 V)                                                                |               | 20            | _             | mA   |

| @200 MHz (CMOS)                      |                   | CML (3.3 V)                                                                 | _             | 35            | _             | mA   |

|                                      |                   | HCSL, 100 MHz, 2 pF load (3.3 V)                                            |               | 35            | _             | mA   |

|                                      |                   | CMOS (1.8 V, SFOUT = Open/0),<br>per output, C <sub>L</sub> = 5 pF, 200 MHz | —             | 5             | _             | mA   |

|                                      |                   | CMOS (2.5 V, SFOUT = Open/0),<br>per output, C <sub>L</sub> = 5 pF, 200 MHz |               | 8             | _             | mA   |

|                                      |                   | CMOS (3.3 V, SFOUT = $0/1$ ), per output, C <sub>L</sub> = 5 pF, 200 MHz    | _             | 15            | _             | mA   |

| Input Clock Voltage<br>Reference     | $V_{REF}$         | V <sub>REF</sub> pin<br>I <sub>REF</sub> = +/-500 μA                        |               | VDD/2         | _             | V    |

| Input High Voltage                   | V <sub>IH</sub>   | SFOUTx,<br>CLK_SEL, OEx                                                     | 0.8 x<br>VDD  | _             | _             | V    |

| Input Mid Voltage                    | $V_{IM}$          | SFOUTx,<br>3-level input pins                                               | 0.45 x<br>VDD | 0.5 x<br>VDD  | 0.55 x<br>VDD | V    |

| Input Low Voltage                    | $V_{IL}$          | SFOUTx,<br>CLK_SEL, OEx                                                     |               | _             | 0.2 x<br>VDD  | V    |

| Internal Pull-down<br>Resistor       | R <sub>DOWN</sub> | CLK_SEL, SFOUTx                                                             | <u>—</u>      | 25            | _             | kΩ   |

| Internal Pull-up<br>Resistor         | $R_{UP}$          | OEx, SFOUTx                                                                 | _             | 25            | _             | kΩ   |

| *Note: Low-power LVP                 | ECL mode sup      | ports an output termination scheme that w                                   | rill reduce o | verall syster | n power.      |      |

#### **Table 4. Output Characteristics (LVPECL)**

$(V_{DDOX} = 2.5 \text{ V} \pm 5\%, \text{ or } 3.3 \text{ V} \pm 10\%, TA = -40 \text{ to } 85 \text{ °C})$

| Parameter                                                                          | Symbol           | Test Condition | Min                       | Тур  | Max                       | Unit |  |

|------------------------------------------------------------------------------------|------------------|----------------|---------------------------|------|---------------------------|------|--|

| Output DC Common Mode<br>Voltage                                                   | V <sub>COM</sub> |                | V <sub>DDOX</sub> – 1.595 | _    | V <sub>DDOX</sub> – 1.245 | V    |  |

| Single-Ended<br>Output Swing*                                                      | $V_{SE}$         |                | 0.40                      | 0.80 | 1.050                     | V    |  |

| *Note: Unused outputs can be left floating. Do not short unused outputs to ground. |                  |                |                           |      |                           |      |  |

# **Table 5. Output Characteristics (Low Power LVPECL)**

$(V_{DDOX} = 2.5 \text{ V} \pm 5\%, \text{ or } 3.3 \text{ V} \pm 10\%, \text{TA} = -40 \text{ to } 85 \text{ °C})$

| Parameter                        | Symbol           | Test Condition                                    | Min                       | Тур  | Max                       | Unit |

|----------------------------------|------------------|---------------------------------------------------|---------------------------|------|---------------------------|------|

| Output DC Common<br>Mode Voltage | V <sub>COM</sub> | $R_L$ = 100 $Ω$ across $Q$ n and $\overline{Q}$ n | V <sub>DDOX</sub> – 1.895 |      | V <sub>DDOX</sub> – 1.275 | V    |

| Single-Ended<br>Output Swing     | V <sub>SE</sub>  | $R_L$ = 100 $Ω$ across $Q$ n and $\overline{Q}$ n | 0.20                      | 0.60 | 0.85                      | V    |

#### Table 6. Output Characteristics—CML

(V<sub>DDOX</sub> = 1.8 V  $\pm$  5%, 2.5 V  $\pm$  5%, or 3.3 V  $\pm$  10%, T<sub>A</sub> = –40 to 85 °C)

| Parameter                    | Symbol   | Test Condition                                     | Min | Тур | Max | Unit |

|------------------------------|----------|----------------------------------------------------|-----|-----|-----|------|

| Single-Ended Output<br>Swing | $V_{SE}$ | Terminated as shown in Figure 8 (CML termination). | 200 | 400 | 550 | mV   |

## Table 7. Output Characteristics—LVDS

$(V_{DDOX} = 1.8 \text{ V} \pm 5\%, 2.5 \text{ V} \pm 5\%, \text{ or } 3.3 \text{ V} \pm 10\%, T_A = -40 \text{ to } 85 \text{ °C})$

| Parameter                                                              | Symbol            | Test Condition                                                                                                   | Min  | Тур  | Max  | Unit |

|------------------------------------------------------------------------|-------------------|------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| Single-Ended Output<br>Swing                                           | V <sub>SE</sub>   | $R_L$ = 100 $\Omega$ across $Q_N$ and $\overline{Q}_N$                                                           | 200  | _    | 490  | mV   |

| Output Common<br>Mode Voltage<br>(V <sub>DDO</sub> = 2.5 V or<br>3.3V) | V <sub>COM1</sub> | $V_{DDOX}$ = 2.38 to 2.63 V, 2.97 to 3.63 V, R <sub>L</sub> = 100 Ω across Q <sub>N</sub> and $\overline{Q}_{N}$ | 1.10 | 1.25 | 1.35 | V    |

| Output Common<br>Mode Voltage<br>(V <sub>DDO</sub> = 1.8 V)            | V <sub>COM2</sub> | $V_{DDOX}$ = 1.71 to 1.89 V,<br>$R_L$ = 100 Ω <u>across</u> $Q_N$<br>and $Q_N$                                   | 0.85 | 0.97 | 1.25 | V    |

#### Table 8. Output Characteristics—LVCMOS

(V<sub>DDOX</sub> = 1.8 V  $\pm$  5%, 2.5 V  $\pm$  5%, or 3.3 V  $\pm$  10%, T<sub>A</sub> = –40 to 85 °C)

| Parameter                                                                                     | Symbol          | Test Condition | Min                      | Тур | Max                      | Unit |  |

|-----------------------------------------------------------------------------------------------|-----------------|----------------|--------------------------|-----|--------------------------|------|--|

| Output Voltage High <sup>*</sup>                                                              | V <sub>OH</sub> |                | 0.75 x V <sub>DDOX</sub> |     | _                        | ٧    |  |

| Output Voltage Low <sup>*</sup>                                                               | V <sub>OL</sub> |                | _                        |     | 0.25 x V <sub>DDOX</sub> | V    |  |

| *Note: IOH and IOH per the Output Signal Format Table for specific VDDOV and SFOUTX settings. |                 |                |                          |     |                          |      |  |

#### Table 9. Output Characteristics—HCSL

$(V_{DDOX} = 3.3 V \pm 10\%, T_A = -40 \text{ to } 85 ^{\circ}C))$

| Parameter                    | Symbol          | Test Condition             | Min  | Тур | Max | Unit |

|------------------------------|-----------------|----------------------------|------|-----|-----|------|

| Output Voltage High          | V <sub>OH</sub> | $R_L = 50 \Omega$ to GND   | 550  | 700 | 900 | mV   |

| Output Voltage Low           | V <sub>OL</sub> | $R_L = 50 \Omega$ to GND   | -150 | 0   | 150 | mV   |

| Single-Ended<br>Output Swing | V <sub>SE</sub> | $R_L$ = 50 $\Omega$ to GND | 450  | 700 | 850 | mV   |

| Crossing Voltage             | V <sub>C</sub>  | $R_L$ = 50 $\Omega$ to GND | 250  | 350 | 550 | mV   |

#### **Table 10. AC Characteristics**

$(V_{DD} = V_{DDOX} = 1.8 \text{ V} \pm 5\%, 2.5 \text{ V} \pm 5\%, \text{ or } 3.3 \text{ V} \pm 10\%, T_A = -40 \text{ to } 85 \text{ °C})$

| Parameter                               | Symbol         | Test Condition                                                                       | Min  | Тур | Max  | Unit |

|-----------------------------------------|----------------|--------------------------------------------------------------------------------------|------|-----|------|------|

| Frequency                               | F              | LVPECL, low power LVPECL, LVDS,<br>CML, HCSL                                         | DC   | _   | 1250 | GHz  |

|                                         |                | LVCMOS                                                                               | DC   | _   | 200  | MHz  |

| Duty Cycle  Note: 50% input duty cycle. | D <sub>C</sub> | 200 MHz, 20/80% T <sub>R</sub> /T <sub>F</sub> <10% of period (LVCMOS) (12 mA drive) | 40   | 50  | 60   | %    |

|                                         |                | 20/80% T <sub>R</sub> /T <sub>F</sub> <10% of period<br>(Differential)               | 47   | 50  | 53   | %    |

| Minimum Input Clock<br>Slew Rate        | SR             | Required to meet prop delay and additive jitter specifications (20–80%)              | 0.75 | _   | _    | V/ns |

- 1. HCSL measurements were made with receiver termination. See Figure 8 on page 17.

- **2.** Output to Output skew specified for outputs with an identical configuration.

- 3. Defined as skew between any output on different devices operating at the same supply voltage, temperature, and and equal load condition. Using the same type of inputs on each device, the outputs are measured at the differential cross points.

- **4.** Measured for 156.25 MHz carrier frequency. Sine-wave noise added to  $V_{DDOX}$  (3.3 V = 100 mV<sub>PP</sub>) and noise spur amplitude measured. See "AN491: Power Supply Rejection for Low-Jitter Clocks" for further details.

**Table 10. AC Characteristics (Continued)**

$(V_{DD} = V_{DDOX} = 1.8 \text{ V} \pm 5\%, 2.5 \text{ V} \pm 5\%, \text{ or } 3.3 \text{ V} \pm 10\%, T_A = -40 \text{ to } 85 \text{ °C})$

| Parameter                          | Symbol                         | Test Condition                       | Min  | Тур         | Max  | Unit |

|------------------------------------|--------------------------------|--------------------------------------|------|-------------|------|------|

| Output Rise/Fall Time              | T <sub>R</sub> /T <sub>F</sub> | LVDS, 20/80%                         | _    | _           | 325  | ps   |

|                                    |                                | LVPECL, 20/80%                       |      | _           | 350  | ps   |

|                                    |                                | HCSL <sup>1</sup> , 20/80%           | _    | _           | 280  | ps   |

|                                    |                                | CML, 20/80%                          | _    | _           | 350  | ps   |

|                                    |                                | Low-Power LVPECL, 20/80%             | _    | _           | 325  | ps   |

|                                    |                                | LVCMOS 200 MHz, 20/80%,<br>2 pF load | _    | _           | 750  | ps   |

| Minimum Input Pulse<br>Width       | T <sub>W</sub>                 |                                      | 360  | _           | _    | ps   |

| Propagation Delay                  | T <sub>PLH,</sub>              | LVCMOS (12mA drive with no load)     | 1250 | 2000        | 2750 | ps   |

|                                    | T <sub>PHL</sub>               | LVPECL                               | 600  | 800         | 1000 | ps   |

|                                    |                                | LVDS                                 | 600  | 800         | 1000 | ps   |

| Output Enable Time                 | T <sub>EN</sub>                | F = 1 MHz                            | _    | 2500        | _    | ns   |

|                                    |                                | F = 100 MHz                          | _    | 30          | _    | ns   |

|                                    |                                | F = 725 MHz                          | _    | 5           | _    | ns   |

| Output Disable Time                | T <sub>DIS</sub>               | F = 1 MHz                            | _    | 2000        | _    | ns   |

|                                    |                                | F = 100 MHz                          |      | 30          | _    | ns   |

|                                    |                                | F = 725 MHz                          |      | 5           | _    | ns   |

| Output to Output Skew <sup>2</sup> | T <sub>SK</sub>                | LVCMOS (12 mA drive to no load)      |      | 50          | 120  | ps   |

|                                    |                                | LVPECL                               | _    | 35          | 70   | ps   |

|                                    |                                | LVDS                                 | _    | 35          | 70   | ps   |

| Part to Part Skew <sup>3</sup>     | T <sub>PS</sub>                | Differential                         | _    | _           | 150  | ps   |

| Power Supply Noise                 | PSRR                           | 10 kHz sinusoidal noise              | _    | -65         | _    | dBc  |

| Rejection <sup>4</sup>             |                                | 100 kHz sinusoidal noise             |      | -63         |      | dBc  |

|                                    |                                | 500 kHz sinusoidal noise             |      | -60         |      | dBc  |

|                                    |                                | 1 MHz sinusoidal noise               | _    | <b>–</b> 55 | _    | dBc  |

- 1. HCSL measurements were made with receiver termination. See Figure 8 on page 17.

- 2. Output to Output skew specified for outputs with an identical configuration.

- 3. Defined as skew between any output on different devices operating at the same supply voltage, temperature, and and equal load condition. Using the same type of inputs on each device, the outputs are measured at the differential cross points.

- **4.** Measured for 156.25 MHz carrier frequency. Sine-wave noise added to  $V_{DDOX}$  (3.3 V = 100 mV<sub>PP</sub>) and noise spur amplitude measured. See "AN491: Power Supply Rejection for Low-Jitter Clocks" for further details.

**Table 11. Additive Jitter, Differential Clock Input**

| V <sub>DD</sub> |                         |              | Input <sup>1,2</sup>                                            | Output                                      | Additive<br>(fs rms, 12<br>20 MF | 2 kHz to |     |

|-----------------|-------------------------|--------------|-----------------------------------------------------------------|---------------------------------------------|----------------------------------|----------|-----|

|                 | Freq Clock Format (MHz) |              | Amplitude<br>V <sub>IN</sub><br>(Single-Ended,<br>Peak-to-Peak) | Differential<br>20%-80% Slew<br>Rate (V/ns) | Clock Format                     | Тур      | Max |

| 3.3             | 725                     | Differential | 0.15                                                            | 0.637                                       | LVPECL                           | 45       | 65  |

| 3.3             | 725                     | Differential | 0.15                                                            | 0.637                                       | LVDS                             | 50       | 65  |

| 3.3             | 156.25                  | Differential | 0.5                                                             | 0.458                                       | LVPECL                           | 160      | 185 |

| 3.3             | 156.25                  | Differential | 0.5                                                             | 0.458                                       | LVDS                             | 150      | 200 |

| 2.5             | 725                     | Differential | 0.15                                                            | 0.637                                       | LVPECL                           | 45       | 65  |

| 2.5             | 725                     | Differential | 0.15                                                            | 0.637                                       | LVDS                             | 50       | 65  |

| 2.5             | 156.25                  | Differential | 0.5                                                             | 0.458                                       | LVPECL                           | 145      | 185 |

| 2.5             | 156.25                  | Differential | 0.5                                                             | 0.458                                       | LVDS                             | 145      | 195 |

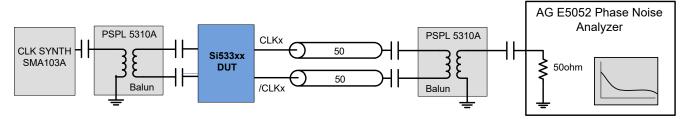

**<sup>1.</sup>** For best additive jitter results, use the fastest slew rate possible. See "AN766: Understanding and Optimizing Clock Buffer's Additive Jitter Performance" for more information.

<sup>2.</sup> AC-coupled differential inputs.

<sup>3.</sup> Measured differentially using a balun at the phase noise analyzer input. See Figure 1.

Table 12. Additive Jitter, Single-Ended Clock Input

| V <sub>DD</sub> |                                                             | ı            | Input <sup>1,2</sup>                                   |                                  | Output              | Additive Jitter<br>(fs rms, 12 kHz to<br>20 MHz) <sup>3</sup> |     |

|-----------------|-------------------------------------------------------------|--------------|--------------------------------------------------------|----------------------------------|---------------------|---------------------------------------------------------------|-----|

|                 | Freq Clock Format (MHz)                                     |              | Amplitude V <sub>IN</sub> (single-ended, peak to peak) | V <sub>IN</sub> Slew Rate (V/ns) |                     | Тур                                                           | Max |

| 3.3             | 200                                                         | Single-ended | 1.70                                                   | 1                                | LVCMOS4             | 120                                                           | 160 |

| 3.3             | 156.25                                                      | Single-ended | 2.18                                                   | 1                                | LVPECL              | 160                                                           | 185 |

| 3.3             | 156.25                                                      | Single-ended | 2.18                                                   | 1                                | LVDS                | 150                                                           | 200 |

| 3.3             | 156.25                                                      | Single-ended | 2.18                                                   | 1                                | LVCMOS4             | 130                                                           | 180 |

| 2.5             | 200                                                         | Single-ended | 1.70                                                   | 1                                | LVCMOS <sup>5</sup> | 120                                                           | 160 |

| 2.5             | 156.25 Single-ended 156.25 Single-ended 156.25 Single-ended |              | 2.18                                                   | 1                                | LVPECL              | 145                                                           | 185 |

| 2.5             |                                                             |              | 2.18                                                   | 1                                | LVDS                | 145                                                           | 195 |

| 2.5             |                                                             |              | 2.18                                                   | 1                                | LVCMOS <sup>5</sup> | 140                                                           | 180 |

- **1.** For best additive jitter results, use the fastest slew rate possible. See "AN766: Understanding and Optimizing Clock Buffer's Additive Jitter Performance" for more information.

- 2. DC-coupled single-ended inputs.

- 3. Measured differentially using a balun at the phase noise analyzer input. See Figure 1.

- **4.** Drive Strength: 12 mA, 3.3 V (SFOUT = 11). LVCMOS jitter is measured single-ended.

- 5. Drive Strength: 9 mA, 2.5 V (SFOUT = 11). LVCMOS jitter is measured single-ended.

Figure 1. Differential Measurement Method Using a Balun

**Table 13. Thermal Conditions**

| Parameter                                  | Symbol            | Test Condition | Value | Unit |

|--------------------------------------------|-------------------|----------------|-------|------|

| Thermal Resistance,<br>Junction to Ambient | $\theta_{JA}$     | Still air      | 49.6  | °C/W |

| Thermal Resistance,<br>Junction to Case    | $\theta_{\sf JC}$ | Still air      | 32.3  | °C/W |

# **Table 14. Absolute Maximum Ratings**

| Parameter                            | Symbol            | Test Condition                                     | Min         | Тур | Max                   | Unit |

|--------------------------------------|-------------------|----------------------------------------------------|-------------|-----|-----------------------|------|

| Storage Temperature                  | T <sub>S</sub>    |                                                    | <b>-</b> 55 | _   | 150                   | °C   |

| Supply Voltage                       | V <sub>DD</sub>   |                                                    | -0.5        | _   | 3.8                   | V    |

| Input Voltage                        | V <sub>IN</sub>   |                                                    | -0.5        | _   | V <sub>DD</sub> + 0.3 | V    |

| Output Voltage                       | V <sub>OUT</sub>  |                                                    | _           | _   | V <sub>DD</sub> + 0.3 | V    |

| ESD Sensitivity                      | HBM               | HBM, 100 pF, 1.5 kΩ                                | _           | _   | 2000                  | V    |

| ESD Sensitivity                      | CDM               |                                                    | _           | _   | 500                   | V    |

| Peak Soldering<br>Reflow Temperature | T <sub>PEAK</sub> | Pb-Free; Solder reflow profile per JEDEC J-STD-020 | _           | _   | 260                   | °C   |

| Maximum Junction<br>Temperature      | T <sub>J</sub>    |                                                    | _           | _   | 125                   | °C   |

**Note:** Stresses beyond those listed in this table may cause permanent damage to the device. Functional operation specification compliance is not implied at these conditions. Exposure to maximum rating conditions for extended periods may affect device reliability.

# 2. Functional Description

The Si53314 is a low jitter, low skew 1:6 differential buffer with an integrated 2:1 input mux and individual OE control. The device has a universal input that accepts most common differential or LVCMOS input signals. A clock select pin control is used to select the active input clock. The selected clock input is routed to two independent banks of outputs. Each output bank features control pins to select signal format setting and LVCMOS drive strength. In addition, each clock output has an independent OE pin for individual clock enable/disable.

#### 2.1. Universal, Any-Format Input

The universal input stage enables simple interfacing to a wide variety of clock formats, including LVPECL, low-power LVPECL, LVCMOS, LVDS, HCSL, and CML. Tables 15 and 16 summarize the various ac- and dc-coupling options supported by the device. For the best high-speed performance, the use of differential formats is recommended. For both single-ended and differential input clocks, the fastest possible slew rate is recommended as low slew rates can increase the noise floor and degrade jitter performance. Though not required, a minimum slew rate of 0.75 V/ns is recommended for differential formats and 1.0 V/ns for single-ended formats. See "AN766: Understanding and Optimizing Clock Buffer's Additive Jitter Performance" for more information.

|           | LVPECL AC-Couple DC-Couple |     | LVC       | LVCMOS    |           | LVDS      |  |

|-----------|----------------------------|-----|-----------|-----------|-----------|-----------|--|

|           |                            |     | AC-Couple | DC-Couple | AC-Couple | DC-Couple |  |

| 1.8 V     | N/A                        | N/A | No        | No        | Yes       | No        |  |

| 2.5/3.3 V | Yes                        | Yes | No        | Yes       | Yes       | Yes       |  |

Table 15. LVPECL, LVCMOS, and LVDS Input Clock Options

Table 16. HCSL and CML Input Clock Options

|           | HCSL                |             | CI        | ИL        |

|-----------|---------------------|-------------|-----------|-----------|

|           | AC-Couple DC-Couple |             | AC-Couple | DC-Couple |

| 1.8 V     | No                  | No          | Yes       | No        |

| 2.5/3.3 V | Yes (3.3 V)         | Yes (3.3 V) | Yes       | No        |

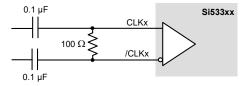

Figure 2. Differential HCSL, LVPECL, Low-Power LVPECL, LVDS, CML AC-Coupled Input Termination

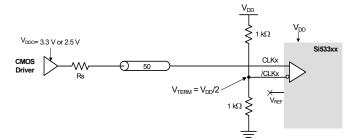

Figure 3. LVCMOS DC-Coupled Input Termination

Note: 33 Ohm series termination is optional depending on the location of the receiver.

Figure 4. Differential DC-Coupled Input Terminations

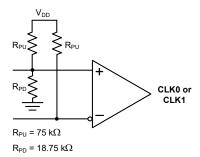

## 2.2. Input Bias Resistors

Internal bias resistors ensure a differential output low condition in the event that the clock inputs are not connected. The non-inverting input is biased with a 18.75 k $\Omega$  pull-down to GND and a 75 k $\Omega$  pull-up to V<sub>DD</sub>. The inverting input is biased with a 75 k $\Omega$  pull-up to V<sub>DD</sub>.

Figure 5. Input Bias Resistors

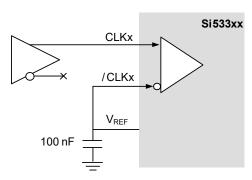

# 2.3. Input Clock Voltage Reference (V<sub>REF</sub>)

The  $V_{REF}$  pin is used to bias the input receiver when a differential input clock is terminated as a single-ended reference clock to the device. Connect the single-ended input to either CLK0 or CLK1. Use the recommended input termination and bias circuit as shown in Figure 3. Note that the  $V_{REF}$  pin should be left floating when LVCMOS or differential clocks are used.

Figure 6. Using Voltage Reference with Single-Ended Input Clock

## 2.4. Universal, Any-Format Output Buffer

The highly flexible output drivers support a wide range of clock signal formats, including LVPECL, low power LVPECL, LVDS, CML, HCSL, and LVCMOS. SFOUTx[1] and SFOUTx[0] are 3-level inputs that can be pin-strapped to select the Bank A and Bank B clock signal formats independently. This feature enables the device to be used for format translation in addition to clock distribution, minimizing the number of unique buffer part numbers required in a typical application and simplifying design reuse. For EMI reduction applications, four LVCMOS drive strength options are available for each  $V_{\rm DDO}$  setting.

**Table 17. Output Signal Format Selection**

| SFOUTX[1] | SFOUTX[0]         | V <sub>DDOX</sub> = 3.3 V | V <sub>DDOX</sub> = 2.5 V | $V_{DDOX} = 1.8 V$  |

|-----------|-------------------|---------------------------|---------------------------|---------------------|

| Open*     | pen* Open* LVPECL |                           | LVPECL                    | N/A                 |

| 0         | 0 0 LVDS          |                           | LVDS                      | LVDS                |

| 0         | 1                 | LVCMOS, 24 mA drive       | LVCMOS, 18 mA drive       | LVCMOS, 12 mA drive |

| 1         | 0                 | LVCMOS, 18 mA drive       | LVCMOS, 12 mA drive       | LVCMOS, 9 mA drive  |

| 1         | 1                 | LVCMOS, 12 mA drive       | LVCMOS, 9 mA drive        | LVCMOS, 6 mA drive  |

| Open*     | 0                 | LVCMOS, 6 mA drive        | LVCMOS, 4 mA drive        | LVCMOS, 2 mA drive  |

| Open*     | 1                 | LVPECL low power          | LVPECL low power          | N/A                 |

| 0 Open*   |                   | CML                       | CML                       | CML                 |

| 1 Open*   |                   | HCSL                      | N/A                       | N/A                 |

\*Note: SFOUTx are 3-level input pins. Tie low for "0" setting. Tie high for "1" setting. When left open, the pin floats to  $V_{DD}/2$ .

# 2.5. Input Mux and Output Enable Logic

Two clock inputs for applications that need to select between one of two clock sources. The CLK\_SEL pin selects the active clock input. The table below summarizes the input and output clock based on the input mux and output enable pin settings.

**Table 18. Input Mux and Output Enable Logic**

| CLK_SEL | CLK0 | CLK1 | OE <sup>1</sup> | Q <sup>2</sup> |

|---------|------|------|-----------------|----------------|

| L       | L    | Х    | Н               | L              |

| L       | Н    | Х    | Н               | Н              |

| Н       | Х    | L    | Н               | L              |

| Н       | Х    | Н    | Н               | Н              |

| Х       | Х    | Х    | L               | L <sup>3</sup> |

#### Notes:

- 1. Output enable active high

- 2. On the next negative transition of CLK0 or CLK1.

- 3. Single-end: Q = low,  $\overline{Q} = low$ Differential: Q = low,  $\overline{Q} = high$

# 2.6. Power Supply ( $V_{DD}$ and $V_{DDOX}$ )

The device includes separate core ( $V_{DD}$ ) and output driver supplies ( $V_{DDOX}$ ). This feature allows the core to operate at a lower voltage than  $V_{DDO}$ , reducing current consumption in mixed supply applications. The core  $V_{DD}$  supports 3.3 V, 2.5 V, or 1.8 V. Each output bank has its own  $V_{DDOX}$  supply, supporting 3.3 V, 2.5 V, or 1.8 V.

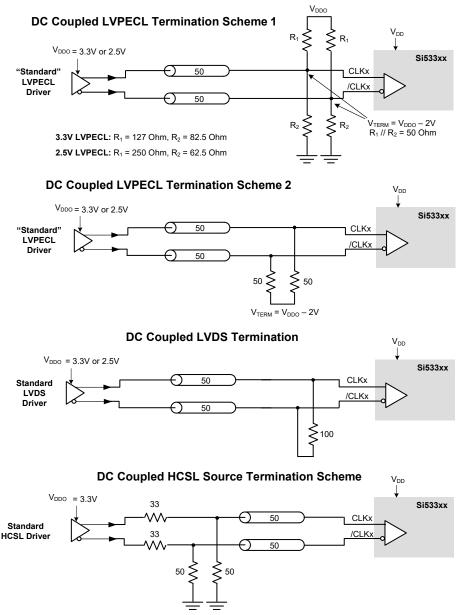

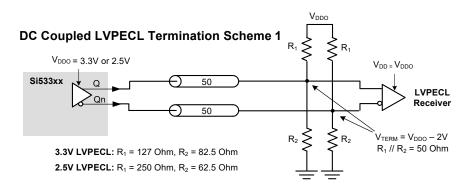

# 2.7. Output Clock Termination Options

The recommended output clock termination options are shown below.

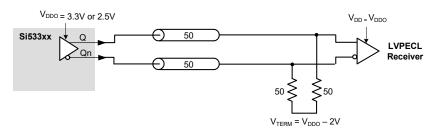

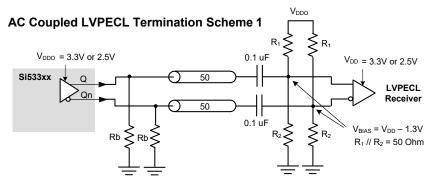

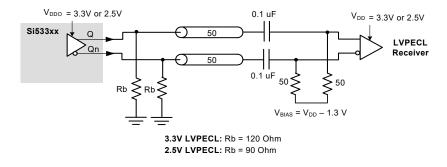

#### **DC Coupled LVPECL Termination Scheme 2**

**3.3V LVPECL:** R<sub>1</sub> = 82.5 Ohm, R<sub>2</sub> = 127 Ohm, Rb = 120 Ohm **2.5V LVPECL:** R<sub>1</sub> = 62.5 Ohm, R<sub>2</sub> = 250 Ohm, Rb = 90 Ohm

#### AC Coupled LVPECL Termination Scheme 2

Figure 7. LVPECL Output Termination

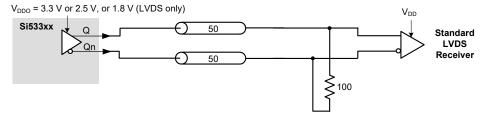

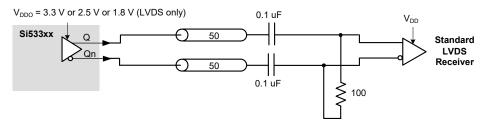

# **DC Coupled LVDS and Low-Power LVPECL Termination**

#### AC Coupled LVDS and Low-Power LVPECL Termination

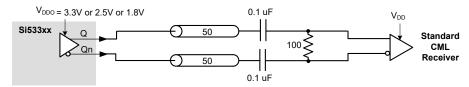

#### **AC Coupled CML Termination**

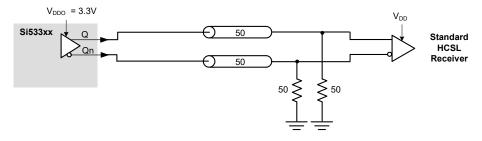

#### **DC Coupled HCSL Receiver Termination**

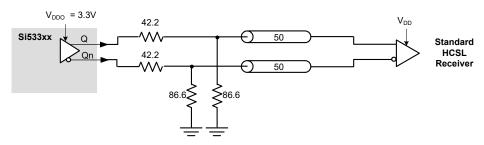

#### **DC Coupled HCSL Source Termination**

Figure 8. LVDS, CML, HCSL, and Low-Power LVPECL Output Termination

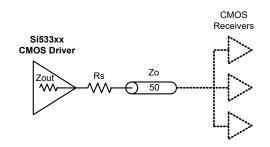

Figure 9. LVCMOS Output Termination

Table 19. Recommended LVCMOS R<sub>S</sub> Series Termination

| SFOUTX[1] | SFOUTX[0] | R <sub>S</sub> (ohms) |       |       |  |

|-----------|-----------|-----------------------|-------|-------|--|

|           |           | 3.3 V                 | 2.5 V | 1.8 V |  |

| 0         | 1         | 33                    | 33    | 33    |  |

| 1         | 0         | 33                    | 33    | 33    |  |

| 1         | 1         | 33                    | 33    | 0     |  |

| Open      | 0         | 0                     | 0     | 0     |  |

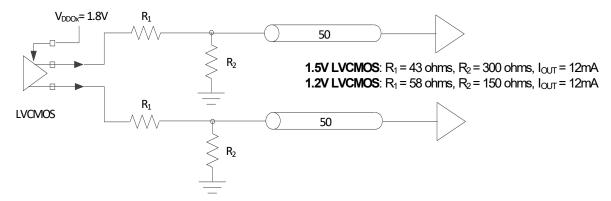

#### 2.7.1. LVCMOS Output Termination To Support 1.5 and 1.2 V

LVCMOS clock outputs are natively supported at 1.8, 2.5, and 3.3 V. However, 1.2 and 1.5V LVCMOS clock outputs can be supported via a simple resistor divider network that will translate the buffer's 1.8V output to a lower voltage as shown in Figure 10.

Figure 10. 1.5V and 1.2V LVCMOS Low-Voltage Output Termination

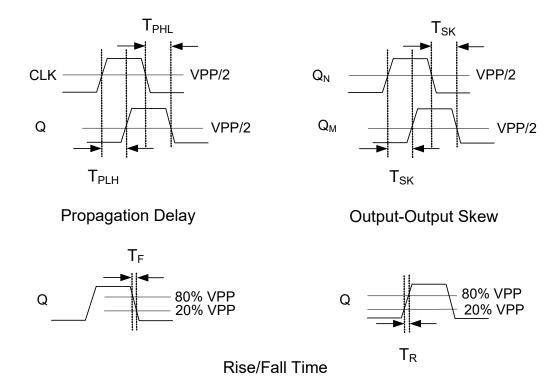

# 2.8. AC Timing Waveforms

Figure 11. AC Waveforms

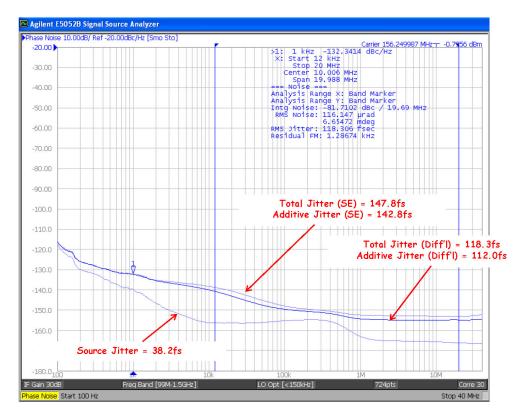

## 2.9. Typical Phase Noise Performance

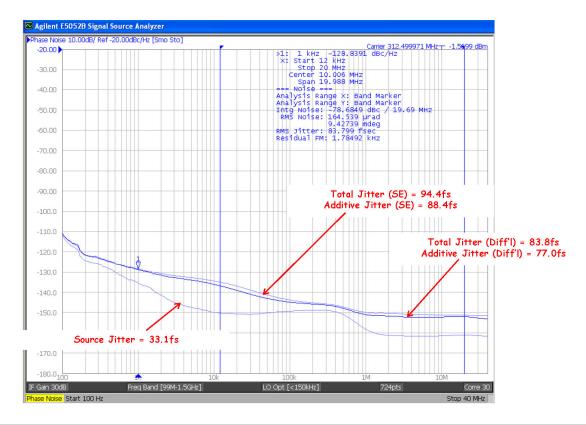

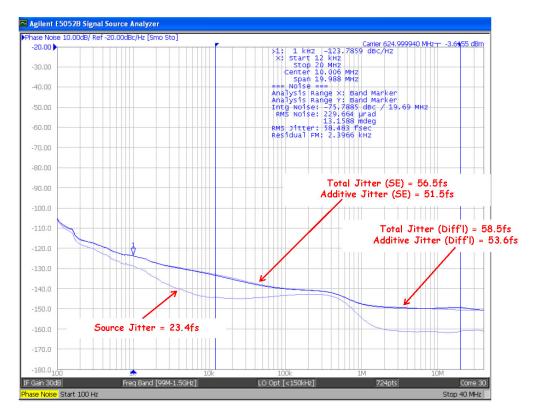

Each of the following three figures shows three phase noise plots superimposed on the same diagram.

**Source Jitter**: Reference clock phase noise.

**Total Jitter (SE)**: Combined source and clock buffer phase noise measured as a single-ended output to the phase noise analyzer and integrated from 12 kHz to 20 MHz.

**Total Jitter (Diff)**: Combined source and clock buffer phase noise measured as a differential output to the phase noise analyzer and integrated from 12 kHz to 20 MHz. The differential measurement as shown in each figure is made using a balun. See Figure 1 on page 9.

Note: To calculate the total RMS phase jitter when adding a buffer to your clock tree, use the root-sum-square (RSS).

The total jitter is a measure of the source plus the buffer's additive phase jitter. The additive jitter (rms) of the buffer can then be calculated (via root-sum-square addition).

| Frequency<br>(MHz) | Diff'l Input<br>Slew Rate<br>(V/ns) | Source<br>Jitter<br>(fs) | Total Jitter<br>(SE)<br>(fs) | Additive Jitter<br>(SE)<br>(fs) | Total Jitter (Diff'l)<br>(fs) | Additive Jitter<br>(Diff'l)<br>(fs) |

|--------------------|-------------------------------------|--------------------------|------------------------------|---------------------------------|-------------------------------|-------------------------------------|

| 156.25             | 1.0                                 | 38.2                     | 147.8                        | 142.8                           | 118.3                         | 112.0                               |

Figure 12. Source Jitter (156.25 MHz)

| Frequency<br>(MHz) | Diff'l Input<br>Slew Rate<br>(V/ns) | Source<br>Jitter<br>(fs) | Total Jitter<br>(SE)<br>(fs) | Additive Jitter<br>(SE)<br>(fs) | Total Jitter (Diff'l)<br>(fs) | Additive Jitter<br>(Diff'l)<br>(fs) |

|--------------------|-------------------------------------|--------------------------|------------------------------|---------------------------------|-------------------------------|-------------------------------------|

| 312.5              | 1.0                                 | 33.10                    | 94.39                        | 88.39                           | 83.80                         | 76.99                               |

Figure 13. Single-Ended Total Jitter (312.5 MHz)

| Frequency<br>(MHz) | Diff'l Input<br>Slew Rate<br>(V/ns) | Source<br>Jitter<br>(fs) | Total Jitter<br>(SE)<br>(fs) | Additive Jitter<br>(SE)<br>(fs) | Total Jitter (Diff'l)<br>(fs) | Additive Jitter<br>(Diff'l)<br>(fs) |

|--------------------|-------------------------------------|--------------------------|------------------------------|---------------------------------|-------------------------------|-------------------------------------|

| 625                | 1.0                                 | 23.4                     | 56.5                         | 51.5                            | 58.5                          | 53.6                                |

Figure 14. Differential Total Jitter (625 MHz)

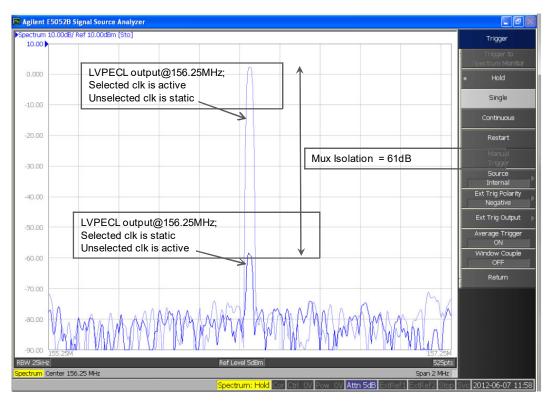

## 2.10. Input Mux Noise Isolation

The buffer's input clock mux is designed to minimize crosstalk between the CLK0 and CLK1. This improves phase jitter performance when clocks are present at both the CLK0 and CLK1 inputs. Figure 15 below is a measurement the input mux's noise isolation.

Figure 15. Input Mux Noise Isolation

# 2.11. Power Supply Noise Rejection

The device supports on-chip supply voltage regulation to reject noise present on the power supply, simplifying low jitter operation in real-world environments. This feature enables robust operation alongside FPGAs, ASICs and SoCs and may reduce board-level filtering requirements. For more information, see "AN491: Power Supply Rejection for Low Jitter Clocks".

# 3. Pin Descriptions

**Table 20. Pin Description**

| Pin | Name      | Type* | Description                                                                                                                                                                                                                                                             |  |

|-----|-----------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1   | OE0       | I     | Output enable—Output 0 When OE = high, the Q0 is enabled. When OE = low, Q is held low and $\overline{Q}$ is held high for differential formats. For LVCMOS, both Q and $\overline{Q}$ are held low when OE is set low. This pin contains an internal pull-up resistor. |  |

| 2   | SFOUTA[1] | I     | Output signal format control pin for Bank A Three level input control. Internally biased at $V_{DD}/2$ . Can be left floating or tied to ground or $V_{DD}$ .                                                                                                           |  |

| 3   | SFOUTA[0] | I     | Output signal format control pin for Bank A Three level input control. Internally biased at $V_{DD}/2$ . Can be left floating or tied to ground or $V_{DD}$ .                                                                                                           |  |

| 4   | Q0        | 0     | Output clock 0 (complement)                                                                                                                                                                                                                                             |  |

| 5   | Q0        | 0     | Output clock 0                                                                                                                                                                                                                                                          |  |

| 6   | GND       | 0     | Ground                                                                                                                                                                                                                                                                  |  |

Table 20. Pin Description (Continued)

| Pin | Name             | Type* | Description                                                                                                                                                                                                                                                                                                                                                |  |

|-----|------------------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 7   | $V_{DD}$         | Р     | Core voltage supply Bypass with 1.0 $\mu\text{F}$ capacitor and place as close to the $V_{DD}$ pin as possible.                                                                                                                                                                                                                                            |  |

| 8   | CLK_SEL          | I     | Mux input select pin (LVCMOS) When CLK_SEL is high, CLK1 is selected. When CLK_SEL is low, CLK0 is selected. CLK_SEL contains an internal pull-down resistor.                                                                                                                                                                                              |  |

| 9   | OE1              | I     | Output enable—Output 1 When OE = high, the Q1 is enabled. When OE = low, Q is held low and $\overline{Q}$ is held high for differential formats. For LVCMOS, both Q and $\overline{Q}$ are held low when OE is set low. This pin contains an internal pull-up resistor.                                                                                    |  |

| 10  | CLK0             | I     | Input clock 0                                                                                                                                                                                                                                                                                                                                              |  |

| 11  | CLK0             | I     | Input clock 0 (complement) When the CLK0 is driven by a single-end input, connect CLK0 to Vdd/2.                                                                                                                                                                                                                                                           |  |

| 12  | OE2              | I     | Output enable—Output 2 When OE = high, the Q2 is enabled. When OE = low, Q is held low and $\overline{Q}$ is held high for differential formats. For LVCMOS, both Q and $\overline{Q}$ are held low when OE is set low. OE2 contains an internal pull-up resistor.                                                                                         |  |

| 13  | OE3              | I     | Output enable—Output 3 When OE = high, the Q3 is enabled. When OE = low, Q is held low and $\overline{Q}$ is held high for differential formats. For LVCMOS, both Q and $\overline{Q}$ are held low when OE is set low. OE3 contains an internal pull-up resistor.                                                                                         |  |

| 14  | CLK1             | I     | Input clock 1                                                                                                                                                                                                                                                                                                                                              |  |

| 15  | CLK1             | I     | Input clock 1 (complement) When the CLK1 is driven by a single-end input, connect CLK1 to Vdd/2.                                                                                                                                                                                                                                                           |  |

| 16  | OE4              | I     | Output enable—Output 4 When OE = high, the Q4 is enabled. When OE = low, Q is held low and $\overline{Q}$ is held high for differential formats. For LVCMOS, both Q and $\overline{Q}$ are held low when OE is set low. This pin contains an internal pull-up resistor.                                                                                    |  |

| 17  | V <sub>REF</sub> | 0     | Input clock reference voltage used to bias CLK0 or CLK1 clock input pins. V <sub>REF</sub> is required when a differential input clock is applied to the device and terminated as a single-ended reference. V <sub>REF</sub> may be left unconnected for LVCMOS or differential clock inputs. See "2.3. Input Clock Voltage Reference (VREF)" for details. |  |

| 18  | $V_{ m DDOA}$    | Р     | Output voltage supply—Bank A (Outputs: Q0 to Q2) Bypass with 1.0 $\mu$ F capacitor and place as close to the V <sub>DDOA</sub> pin as possible.                                                                                                                                                                                                            |  |

Table 20. Pin Description (Continued)

| Pin        | Name           | Type* | Description                                                                                                                                                                                                                                                             |  |

|------------|----------------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 19         | $V_{\rm DDOB}$ | Р     | Output voltage supply—Bank B (Outputs: Q3 to Q5) Bypass with 1.0 $\mu F$ capacitor and place as close to the $V_{DDOB}$ pin as possible.                                                                                                                                |  |

| 20         | Q5             | 0     | Output clock 5 (complement)                                                                                                                                                                                                                                             |  |

| 21         | Q5             | 0     | Output clock 5                                                                                                                                                                                                                                                          |  |

| 22         | SFOUTB[0]      | I     | Output signal format control pin for Bank B Three level input control. Internally biased at $V_{DD}/2$ . Can be left floating or tied to ground or $V_{DD}$ .                                                                                                           |  |

| 23         | SFOUTB[1]      | I     | Output signal format control pin for Bank B Three level input control. Internally biased at V <sub>DD</sub> /2. Can be left floating or tied to ground or V <sub>DD</sub> .                                                                                             |  |

| 24         | OE5            | I     | Output enable—Output 5 When OE = high, the Q5 is enabled. When OE = low, Q is held low and $\overline{Q}$ is held high for differential formats. For LVCMOS, both Q and $\overline{Q}$ are held low when OE is set low. This pin contains an internal pull-up resistor. |  |

| 25         | Q4             | 0     | Output clock 4 (complement)                                                                                                                                                                                                                                             |  |

| 26         | Q4             | 0     | Output clock 4                                                                                                                                                                                                                                                          |  |

| 27         | Q3             | 0     | Output clock 3 (complement)                                                                                                                                                                                                                                             |  |

| 28         | Q3             | 0     | Output clock 3                                                                                                                                                                                                                                                          |  |

| 29         | Q2             | 0     | Output clock 2 (complement)                                                                                                                                                                                                                                             |  |

| 30         | Q2             | 0     | Output clock 2                                                                                                                                                                                                                                                          |  |

| 31         | Q1             | 0     | Output clock 1 (complement)                                                                                                                                                                                                                                             |  |

| 32         | Q1             | 0     | Output clock 1                                                                                                                                                                                                                                                          |  |

| GND<br>Pad | GND            | GND   | Ground Pad Power supply ground and thermal relief.                                                                                                                                                                                                                      |  |

<sup>\*</sup>Pin types are: I = input, O = output, P = power, GND = ground.

# 4. Ordering Guide

| Part Number   | Package          | PB-Free, ROHS-6 | Temperature  |

|---------------|------------------|-----------------|--------------|

| Si53314-B-GM  | 32-QFN           | Yes             | –40 to 85 °C |

| Si53301/4-EVB | Evaluation Board | Yes             | _            |

# 5. Package Outline

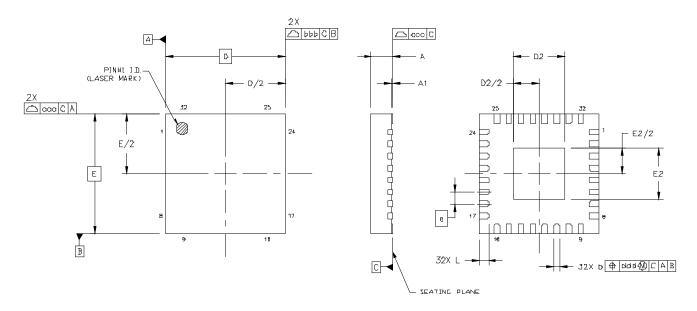

# 5.1. 5x5 mm 32-QFN Package Diagram

Figure 16. Si53314 5x5 mm Package Diagram

| Table: | 21. | <b>Package</b> | <b>Dimensions</b> |

|--------|-----|----------------|-------------------|

|--------|-----|----------------|-------------------|

| Dimension | Min  | Nom      | Max  |  |

|-----------|------|----------|------|--|

| Α         | 0.80 | 0.85     | 1.00 |  |

| A1        | 0.00 | 0.02     | 0.05 |  |

| b         | 0.18 | 0.25     | 0.30 |  |

| С         | 0.20 | 0.25     | 0.30 |  |

| D         |      | 5.00 BSC |      |  |

| D2        | 2.00 | 2.15     | 2.30 |  |

| е         |      | 0.50 BSC |      |  |

| E         |      | 5.00 BSC |      |  |

| E2        | 2.00 | 2.15     | 2.30 |  |

| L         | 0.30 | 0.40     | 0.50 |  |

| aaa       |      | 0.10     |      |  |

| bbb       |      | 0.10     |      |  |

| ccc       |      | 0.08     |      |  |

| ddd       | 0.10 |          |      |  |

| •••       |      |          |      |  |

- 1. All dimensions shown are in millimeters (mm) unless otherwise noted.

- 2. Dimensioning and Tolerancing per ANSI Y14.5M-1994.

- 3. This drawing conforms to the JEDEC Solid State Outline MO-220.

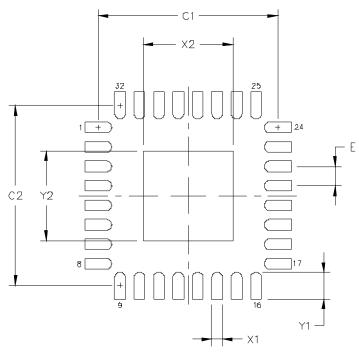

#### 6. PCB Land Pattern

## 6.1. 5x5 mm 32-QFN Package Land Pattern

Figure 17. Si53314 5x5 mm Package Land Pattern

| Dimension | Min      | Max  |

|-----------|----------|------|

| C1        | 4.52     | 4.62 |

| C2        | 4.52     | 4.62 |

| Е         | 0.50 BSC |      |

| X1        | 0.20     | 0.30 |

**Table 22. PCB Land Pattern**

| Dimension | Min  | Max  |

|-----------|------|------|

| X2        | 2.20 | 2.30 |

| Y1        | 0.59 | 0.69 |

| Y2        | 2.20 | 2.30 |

|           |      |      |

#### Notes:

#### General

- 1. All dimensions shown are in millimeters (mm) unless otherwise noted.

- 2. This Land Pattern Design is based on the IPC-7351 guidelines.

#### Solder Mask Design

1. All metal pads are to be non-solder mask defined (NSMD). Clearance between the solder mask and the metal pad is to be  $60 \mu m$  minimum, all the way around the pad.

#### Stencil Design

- **1.** A stainless steel, laser-cut and electro-polished stencil with trapezoidal walls should be used to assure good solder paste release.

- 2. The stencil thickness should be 0.125 mm (5 mils).

- **3.** The ratio of stencil aperture to land pad size should be 1:1 for all perimeter pads.

- 4. A 2x2 array of 0.75 mm square openings on 1.15 mm pitch should be used for the center ground pad.

#### **Card Assembly**

- 1. A No-Clean, Type-3 solder paste is recommended.

- 2. The recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

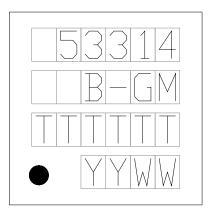

# 7. Top Marking

# 7.1. Si53314 Top Marking

# 7.2. Top Marking Explanation

| Mark Method:    | Laser                                                      |                                                         |

|-----------------|------------------------------------------------------------|---------------------------------------------------------|

| Font Size:      | 2.0 Point (28 mils)<br>Center-Justified                    |                                                         |

| Line 1 Marking: | Device Part Number                                         | 53314                                                   |

| Line 2 Marking: | Device Revision/Type                                       | B-GM                                                    |

| Line 3 Marking: | YY = Year<br>WW = Work Week                                | Corresponds to the year and work week of the mold date. |

|                 | R = Die Rev<br>F = Wafer Fab                               | First two characters of the Manufacturing Code.         |

| Line 4 Marking  | Circle = 0.5 mm Diameter<br>Lower-Left Justified           | Pin 1 Identifier                                        |

|                 | A = Assembly Site I = Internal Code XX = Serial Lot Number | Last four characters of the Manufacturing Code.         |

# **DOCUMENT CHANGE LIST**

# Revision 0.4 to Revision 1.0

- Corrected front-page buffer block diagram.

- Improved performance specifications with greater detail.

- Added additional information to clarify the use of the voltage reference feature.

- Added pin type description to Table 20, "Pin Description," on page 24.

- Added low-voltage termination options for 1.2 V and 1.5 V LVCMOS support.

- Clarified output clock bank A and bank B assignments.

www.skyworksinc.com/CBPro

**Quality** www.skyworksinc.com/quality

**Support & Resources** www.skyworksinc.com/support

#### Copyright © 2021 Skyworks Solutions, Inc. All Rights Reserved.

Information in this document is provided in connection with Skyworks Solutions, Inc. ("Skyworks") products or services. These materials, including the information contained herein, are provided by Skyworks as a service to its customers and may be used for informational purposes only by the customer. Skyworks assumes no responsibility for errors or omissions in these materials or the information contained herein. Skyworks may change its documentation, products, services, specifications or product descriptions at any time, without notice. Skyworks makes no commitment to update the materials or information and shall have no responsibility whatsoever for conflicts, incompatibilities, or other difficulties arising from any future changes.

No license, whether express, implied, by estoppel or otherwise, is granted to any intellectual property rights by this document. Skyworks assumes no liability for any materials, products or information provided hereunder, including the sale, distribution, reproduction or use of Skyworks products, information or materials, except as may be provided in Skyworks' Terms and Conditions of Sale.

THE MATERIALS, PRODUCTS AND INFORMATION ARE PROVIDED "AS IS" WITHOUT WARRANTY OF ANY KIND, WHETHER EXPRESS, IMPLIED, STATUTORY, OR OTHERWISE, INCLUDING FITNESS FOR A PARTICULAR PURPOSE OR USE, MERCHANTABILITY, PERFORMANCE, QUALITY OR NON-INFRINGEMENT OF ANY INTELLECTUAL PROPERTY RIGHT; ALL SUCH WARRANTIES ARE HEREBY EXPRESSLY DISCLAIMED. SKYWORKS DOES NOT WARRANT THE ACCURACY OR COMPLETENESS OF THE INFORMATION, TEXT, GRAPHICS OR OTHER ITEMS CONTAINED WITHIN THESE MATERIALS. SKYWORKS SHALL NOT BE LIABLE FOR ANY DAMAGES, INCLUDING BUT NOT LIMITED TO ANY SPECIAL, INDIRECT, INCIDENTAL, STATUTORY, OR CONSEQUENTIAL DAMAGES, INCLUDING WITHOUT LIMITATION, LOST REVENUES OR LOST PROFITS THAT MAY RESULT FROM THE USE OF THE MATERIALS OR INFORMATION, WHETHER OR NOT THE RECIPIENT OF MATERIALS HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGE.

Skyworks products are not intended for use in medical, lifesaving or life-sustaining applications, or other equipment in which the failure of the Skyworks products could lead to personal injury, death, physical or environmental damage. Skyworks customers using or selling Skyworks products for use in such applications do so at their own risk and agree to fully indemnify Skyworks for any damages resulting from such improper use or sale.

Customers are responsible for their products and applications using Skyworks products, which may deviate from published specifications as a result of design defects, errors, or operation of products outside of published parameters or design specifications. Customers should include design and operating safeguards to minimize these and other risks. Skyworks assumes no liability for applications assistance, customer product design, or damage to any equipment resulting from the use of Skyworks products outside of Skyworks' published specifications or parameters.

Skyworks, the Skyworks symbol, Sky5®, SkyOne®, SkyBlue™, Skyworks Green™, Clockbuilder®, DSPLL®, ISOmodem®, ProSLIC®, and SiPHY® are trademarks or registered trademarks of Skyworks Solutions, Inc. or its subsidiaries in the United States and other countries. Third-party brands and names are for identification purposes only and are the property of their respective owners. Additional information, including relevant terms and conditions, posted at www.skyworksinc.com, are incorporated by reference.