# H13306

December 1997

# 6-Bit, 15 MSPS, Flash A/D Converter

# Features • CMOS Low Power (Typ) .55mW • Parallel Conversion Technique .55mW • Single Power Supply Voltage .3V to 7.5V • Sampling Rate with Single 5V Supply .15MHz • 6-Bit Latched Three-State Output with Overflow Bit .5MHz • Linearity (INL, DNL): .40.5 LSB • HI3306JIP/15 .50.5 LSB • HI3306JIB/16 .50.5 LSB • HI3306JIB/10 .50.5 LSB • Sampling Rate: .15MHz (67ns) • HI3306JIP/10 .10MHz (100ns) • HI3306JIB/15 .15MHz (67ns)

- HI3306JIB/10 . . . . . . . . . . . . . . . . 10MHz (100ns)

# **Applications**

- · Video Digitizing

- Digital Communication Systems

- High Speed Data Acquisition

- Radar Signal Processing

# Description

The HI3306 family are CMOS parallel (FLASH) analog-to-digital converters designed for applications demanding both low power consumption and high speed digitization. Digitizing at 15MHz, for example, requires only about 55mW.

The HI3306 family operates over a wide, full scale signal input voltage range of 1V up to the supply voltage. Power consumption is as low as 15mW, depending upon the clock frequency selected. The HI3306 offers improved linearity at a lower reference voltage and high operating speed with a 5V supply.

The overflow bit makes possible the connection of two or more HI3306s in series to increase the resolution of the conversion system.

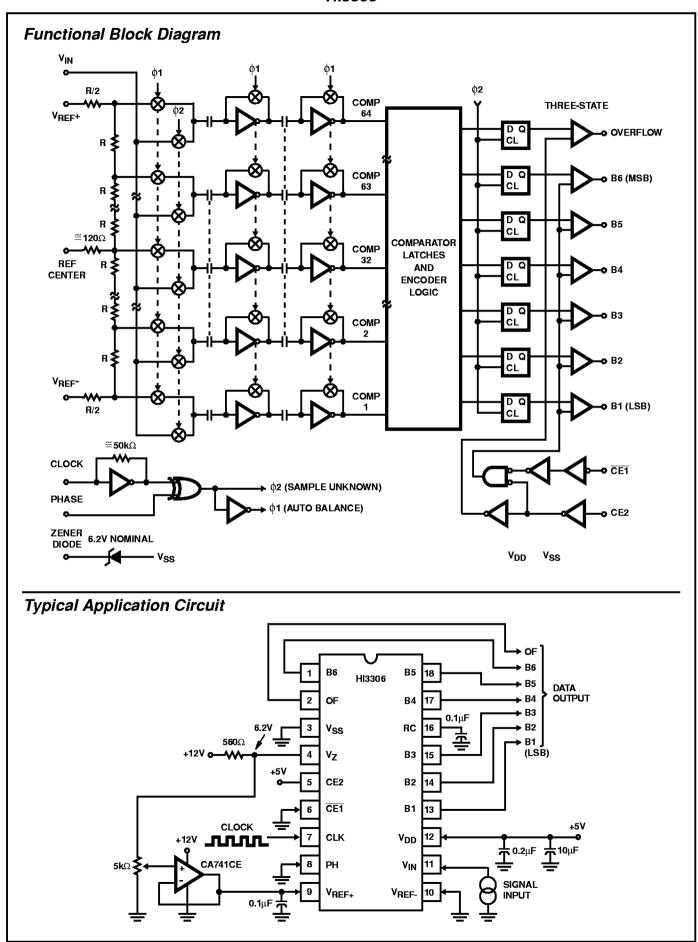

Sixty-four paralleled auto balanced comparators measure the input voltage with respect to a known reference to produce the parallel bit outputs in the HI3306. Sixty-three comparators are required to quantize all input voltage levels in this 6-bit converter, and the additional comparator is required for the overflow bit.

# Ordering Information

| PART NUMBER  | TEMP.<br>RANGE ( <sup>O</sup> C) | PACKAGE    | PKG. NO. |  |  |

|--------------|----------------------------------|------------|----------|--|--|

| HI3306JIP/15 | -40 to 85                        | 18 Ld PDIP | E18.3    |  |  |

| HI3306JIP/10 | -40 to 85                        | 18 Ld PDIP | E18.3    |  |  |

| HI3306JIB/15 | -40 to 85                        | 20 Ld SOIC | M20.3    |  |  |

| HI3306JIB/10 | -40 to 85                        | 20 Ld SOIC | M20.3    |  |  |

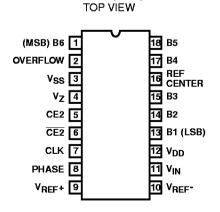

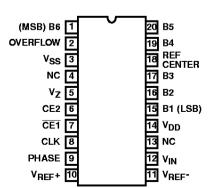

#### **Pinouts**

HI3306 (PDIP)

HI3306 (SOIC)

# HI3306

# Absolute Maximum Ratings Thermal Information

| DC Supply Voltage Range, V <sub>DD</sub>                      |

|---------------------------------------------------------------|

| Voltage Referenced to V <sub>SS</sub> Terminal0.5V to +8.5V   |

| Input Voltage Range                                           |

| All Inputs Except Zener0.5V to V <sub>DD</sub> + 0.5V         |

| DC Input Current                                              |

| CLK, PH, $\overline{\text{CE1}}$ , CE2, V <sub>IN</sub> ±20mA |

| Thermal Resistance (Typical, Note 1)     | θ <sub>JA</sub> (°C/W) |

|------------------------------------------|------------------------|

| PDIP Package                             | 75                     |

| SOIC Package                             | 100                    |

| Maximum Junction Temperature             | 150°C                  |

| Maximum Storage Temperature Range68      | 5°C to 150°C           |

| Maximum Lead Temperature (Soldering 10s) | 300°C                  |

| (SOIC - Lead Tips Only)                  |                        |

# **Operating Conditions**

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

#### NOTE

1.  $\theta_{JA}$  is measured with the component mounted on an evaluation PC board in free air.

$\begin{tabular}{ll} \textbf{Electrical Specifications} & T_A = 25^{o}\text{C}, \ V_{DD} = 5\text{V}, \ V_{REF} + = 4.8\text{V}, \ V_{SS} = V_{REF} - = \text{GND}, \ \text{Clock} = 15\text{MHz Square Wave for HI3306XXX/15}, \ 10\text{MHz for HI3306XXX/10} \\ \end{tabular}$

| PARAMETE                            | R                  | TEST CONDITIONS                                  | MIN  | TYP   | MAX                   | UNITS |

|-------------------------------------|--------------------|--------------------------------------------------|------|-------|-----------------------|-------|

| SYSTEM PERFORMANCE                  |                    |                                                  | •    | •     | '                     |       |

| Resolution                          |                    |                                                  | 6    | -     | -                     | Bits  |

| Integral Linearity Error, INL       |                    |                                                  | -    | ±0.25 | ±0.5                  | LSB   |

| Differential Linearity Error, DN    | L                  |                                                  | -    | ±0.25 | ±0.5                  | LSB   |

| Offset Error (Unadjusted)           |                    | (Note 2)                                         | -    | ±0.5  | ±1                    | LSB   |

| Gain Error (Unadjusted)             |                    | (Note 3)                                         | -    | ±0.5  | ±1                    | LSB   |

| Gain Temperature Coefficient        |                    |                                                  | -    | +0.1  | - 1                   | mV/°C |

| Offset Temperature Coefficien       | t                  |                                                  | -    | -0.1  | -                     | mV/°C |

| DYNAMIC CHARACTERISTIC              | CS Input Signal Le | evel 0.5dB Below Full Scale                      |      | •     | <u> </u>              |       |

| Maximum Conversion Speed            | HI3306XXX/10       |                                                  | 10   | 13    | -                     | MSPS  |

|                                     | HI3306XXX/15       |                                                  | 15   | 20    | - 1                   | MSPS  |

| Maximum Conversion Speed            | HI3306XXX/10       | (Note 5)                                         | 12   | -     | -                     | MSPS  |

|                                     | HI3306XXX/15       | φ1, φ2 ≥ Minimum                                 | 18   | -     | -                     | MSPS  |

| Allowable Input Bandwidth           |                    | (Note 5)                                         | DC   | -     | fCLOCK/2              | MHz   |

| -3dB Input Bandwidth                |                    |                                                  | -    | 30    | -                     | MHz   |

| Signal to Noise Ratio, SNR          |                    | f <sub>S</sub> = 15MHz, f <sub>IN</sub> = 100kHz | -    | 34.6  | -                     | dB    |

| =RMS Signal<br>RMS Noise            |                    | $f_S = 15MHz$ , $f_{IN} = 5MHz$                  | -    | 33.4  | -                     | dB    |

| Signal to Noise Ratio, SINAD        |                    | f <sub>S</sub> = 15MHz, f <sub>IN</sub> = 100kHz | -    | 34.2  | -                     | dB    |

| = RMS Signal RMS Noise + Distortion |                    | $f_S = 15MHz$ , $f_{IN} = 5MHz$                  | -    | 29.0  | -                     | dB    |

| Total Harmonic Distortion, TH       | D                  | f <sub>S</sub> = 15MHz, f <sub>IN</sub> = 100kHz | -    | -46.0 | -                     | dBc   |

|                                     |                    | f <sub>S</sub> = 15MHz, f <sub>IN</sub> = 5MHz   | -    | -30.0 | -                     | dBc   |

| Effective Number of Bits, ENC       | В                  | $f_S = 15MHz$ , $f_{IN} = 100kHz$                | -    | 5.5   | -                     | Bits  |

|                                     |                    | $f_S = 15MHz$ , $f_{IN} = 5MHz$                  | -    | 4.5   | -                     | Bits  |

| ANALOG INPUTS                       |                    |                                                  |      |       |                       |       |

| Positive Full Scale Input Rang      | e                  | (Notes 4, 5)                                     | 1    | 4, 8  | V <sub>DD</sub> + 0.5 | ٧     |

| Negative Full Scale Input Range     |                    | (Notes 4, 5)                                     | -0.5 | 0     | V <sub>DD</sub> - 1   | ٧     |

| Input Capacitance                   |                    |                                                  | -    | 15    | -                     | pF    |

| Input Current                       |                    | V <sub>IN</sub> = 4.92V, V <sub>DD</sub> = 5V    | -    |       | ±500                  | μΑ    |

| INTERNAL VOLTAGE REFE               | RENCE              |                                                  |      |       |                       |       |

| Zener Voltage                       |                    | I <sub>Z</sub> = 10mA                            | 5.4  | 6.2   | 7.4                   | ٧     |

| Zener Dynamic Impedance             |                    | I <sub>Z</sub> = 10mA, 20mA                      | -    | 12    | 25                    | Ω     |

**Electrical Specifications**  $T_A$  = 25°C,  $V_{DD}$  = 5V,  $V_{REF}+$  = 4.8V,  $V_{SS}$  =  $V_{REF}-$  = GND, Clock = 15MHz Square Wave for HI3306XXX/15, 10MHz for HI3306XXX/10 **(Continued)**

| PARAMETER                                |              | TEST CONDITIONS                      | MIN                   | TYP  | MAX                   | UNITS             |  |

|------------------------------------------|--------------|--------------------------------------|-----------------------|------|-----------------------|-------------------|--|

| Zener Temperature Coefficie              | nt           |                                      | -                     | -0.5 | -                     | mV/°C             |  |

| REFERENCE INPUTS                         |              |                                      |                       |      |                       |                   |  |

| Resistor Ladder Impedance                |              |                                      | 650                   | 1100 | 1550                  | Ω                 |  |

| DIGITAL INPUTS                           |              |                                      |                       |      |                       |                   |  |

| Maximum V <sub>IN</sub> , Logic 0        |              | All Digital Inputs (Note 5)          | -                     | -    | 0.3 x V <sub>DD</sub> | ٧                 |  |

| Maximum V <sub>IN</sub> , Logic 1        |              | All Digital Inputs (Note 5)          | 0.7 x V <sub>DD</sub> | -    | -                     | ٧                 |  |

| Digital Input Current                    |              | Except CLK, V <sub>IN</sub> = 0V, 5V | -                     | ±1   | ±5                    | μΑ                |  |

| Digital Input Current                    |              | CLK Only                             | -                     | ±100 | ±200                  | μΑ                |  |

| DIGITAL OUTPUTS                          |              |                                      |                       |      |                       |                   |  |

| Digital Output Three-State Le            | akage        | V <sub>OUT</sub> = 0V, 5V            | -                     | ±1   | ±5                    | μΑ                |  |

| Digital Output Source Curren             | t            | V <sub>OUT</sub> = 4.6V              | -1.6                  | -    | - 1                   | mA                |  |

| Digital Output Sink Current              |              | V <sub>OUT</sub> = 0.4V              | 3.2                   | -    | -                     | mA                |  |

| TIMING CHARACTERISTICS                   | \$           |                                      |                       |      |                       |                   |  |

| Auto Balance Time (φ1)                   | HI3306XXX/10 |                                      | 50                    | -    | ∞                     | ns                |  |

|                                          | HI3306XXX/15 |                                      | 33                    | -    | ∞                     |                   |  |

| Sample Time (¢2)                         | HI3306XXX/10 | (Note 5)                             | 33                    | -    | 5000                  | ns                |  |

|                                          | HI3306XXX/15 | 1                                    | 22                    | -    | 5000                  | ns                |  |

| Aperture Delay                           |              |                                      | -                     | 8    | - 1                   | ns                |  |

| Aperture Jitter                          |              |                                      | -                     | 100  | -                     | ps <sub>P-P</sub> |  |

| Output Data Valid Delay, t <sub>D</sub>  | HI3306XXX/10 |                                      | -                     | 35   | 50                    | ns                |  |

|                                          | HI3306XXX/15 |                                      | -                     | 30   | 40                    | ns                |  |

| Output Data Hold Time, t <sub>H</sub>    |              | (Note 5)                             | 15                    | 25   | -                     | ns                |  |

| Output Enable Time, t <sub>EN</sub>      |              |                                      | -                     | 20   | -                     | ns                |  |

| Output Disable Time, t <sub>DIS</sub>    |              |                                      | -                     | 15   | -                     | ns                |  |

| POWER SUPPLY CHARAC                      | TERISTICS    |                                      |                       |      |                       |                   |  |

| I <sub>DD</sub> Current, Refer to Figure | HI3306XXX/10 | Continuous Conversion (Note 5)       | -                     | 11   | 20                    | mA                |  |

|                                          | HI3306XXX/15 | ]                                    | -                     | 14   | 25                    | mA                |  |

| I <sub>DD</sub> Current                  | _            | Continuous                           | - 1                   | 7.5  | 15                    | mA                |  |

#### NOTES:

- OFFSET ERROR is the difference between the input voltage that causes the 00 to 01 output code transition and (V<sub>REF</sub>+ V<sub>REF</sub>-)/128.

GAIN ERROR is the difference the input voltage that causes the 3F<sub>16</sub> to overflow output code transition and (V<sub>REF</sub>+ V<sub>REF</sub>-) x 127/128.

- 4. The total input voltage range, set by V<sub>REF</sub>+ and V<sub>REF</sub>-, may be in the range of 1 to (V<sub>DD</sub> + 1) V.

- 5. Parameter not tested, but guaranteed by design or characterization.

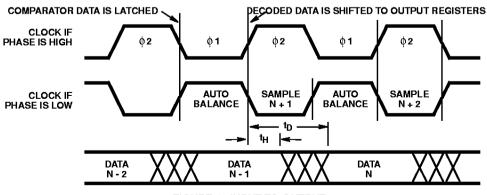

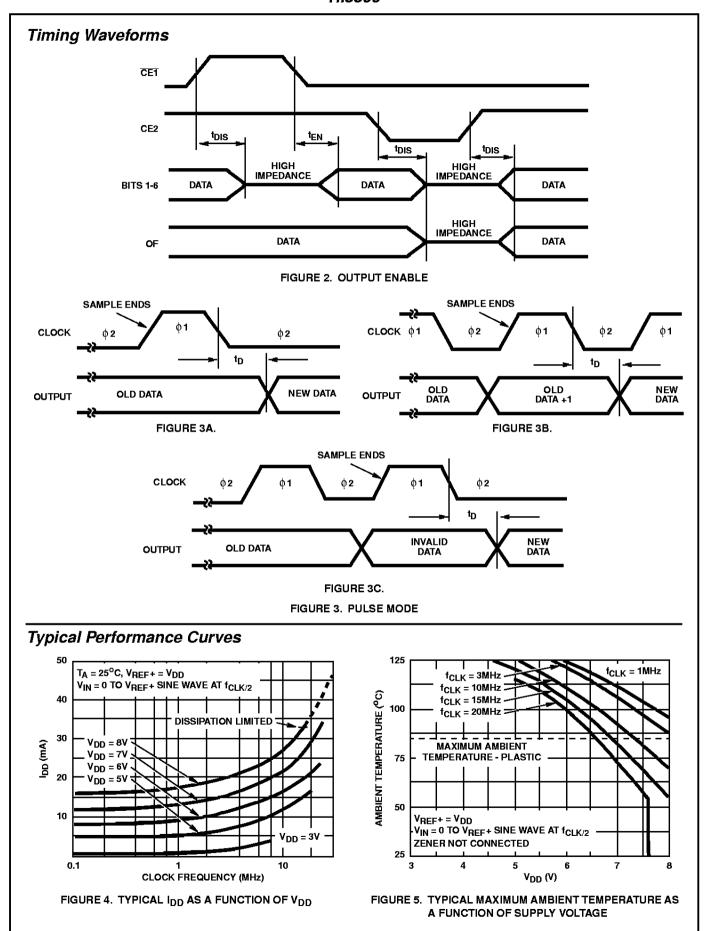

# Timing Waveforms

FIGURE 1. INPUT-TO-OUTPUT

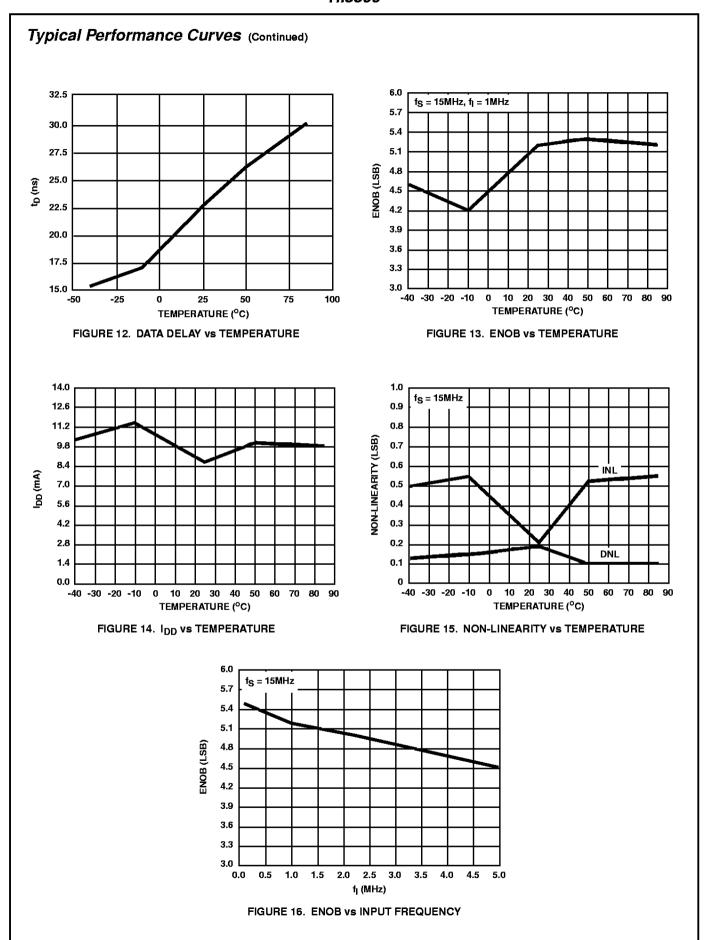

# Typical Performance Curves (Continued)

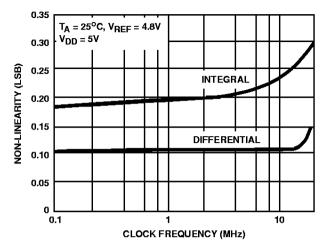

FIGURE 6. TYPICAL NON-LINEARITY AS A FUNCTION OF CLOCK SPEED

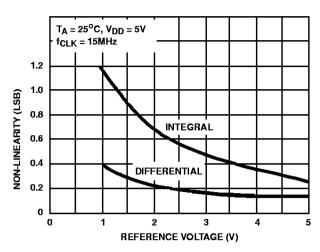

FIGURE 7. TYPICAL NON-LINEARITY AS A FUNCTION OF REFERENCE VOLTAGE

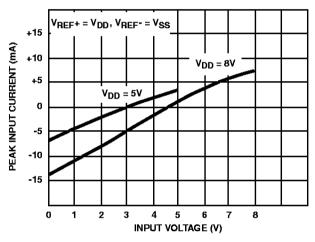

FIGURE 8. TYPICAL PEAK INPUT CURRENT AS A FUNCTION OF INPUT VOLTAGE

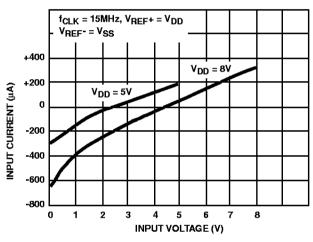

FIGURE 9. TYPICAL AVERAGE INPUT CURRENT AS A FUNCTION OF INPUT VOLTAGE

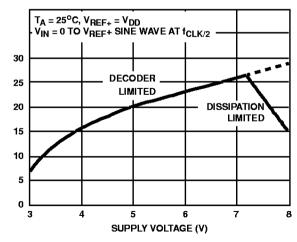

FIGURE 10. TYPICAL MAXIMUM CLOCK FREQUENCY AS A FUNCTION OF SUPPLY VOLTAGE

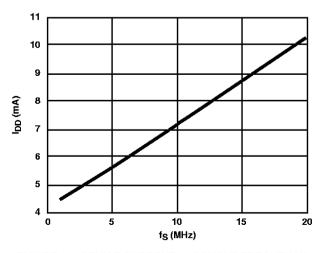

FIGURE 11. DEVICE CURRENT vs SAMPLE FREQUENCY

# Pin Descriptions

| PIN NU | JMBER  |                    |                                                                                                                                                                 |  |

|--------|--------|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| PDIP   | SOIC   | NAME               | DESCRIPTION                                                                                                                                                     |  |

| 1      | 1      | B6                 | Bit 6, Output (MSB).                                                                                                                                            |  |

| 2      | 2      | OF                 | Overflow, Output.                                                                                                                                               |  |

| 3      | 3, 4   | $V_{SS}$           | Digital Ground.                                                                                                                                                 |  |

| 4      | 5      | $V_Z$              | Zener Reference Output.                                                                                                                                         |  |

| 5      | 6      | CE2                | Three-State Output Enable Input, Active Low. See Table 1.                                                                                                       |  |

| 6      | 7      | CE1                | Three-State Output Enable Input, Active High. See Table 1.                                                                                                      |  |

| 7      | 8      | CLK                | Clock Input.                                                                                                                                                    |  |

| 8      | 9      | Phase              | Sample clock phase control input. When PHASE is low, "Sample Unknown" occurs when the clock is low and "Auto Balance" occurs when the clock is high (see text). |  |

| 9      | 10     | V <sub>REF</sub> + | Reference Voltage Positive Input.                                                                                                                               |  |

| 10     | 11     | $V_{REF^{-}}$      | Reference Voltage Negative Input.                                                                                                                               |  |

| 11     | 12     | $V_{IN}$           | Analog Signal Input.                                                                                                                                            |  |

| 12     | 13, 14 | $V_{DD}$           | Power Supply, +5V.                                                                                                                                              |  |

| 13     | 15     | B1                 | Bit 1, Output (LSB).                                                                                                                                            |  |

| 14     | 16     | B2                 | Bit 2, Output.                                                                                                                                                  |  |

| 15     | 17     | В3                 | Bit 3, Output.                                                                                                                                                  |  |

| 16     | 18     | REF(CTR)           | Reference Ladder Midpoint.                                                                                                                                      |  |

| 17     | 19     | B4                 | Bit 4, Output.                                                                                                                                                  |  |

| 18     | 20     | B5                 | Bit 5, Output.                                                                                                                                                  |  |

#### TABLE 1. CHIP ENABLE TRUTH TABLE

| CE1 | CE2 | B1 - B6     | OF          |

|-----|-----|-------------|-------------|

| 0   | 1   | Valid       | Valid       |

| 1   | 1   | Three-State | Valid       |

| Х   | 0   | Three-State | Three-State |

X = Don't care

TABLE 2. OUTPUT CODE TABLE

|                                                |                                 | (NOTE 6) INPUT VOLTAGE BINARY OUTPUT CODE (LSB) |                                 |                                 |    |    |    |    |    |    |    |                  |

|------------------------------------------------|---------------------------------|-------------------------------------------------|---------------------------------|---------------------------------|----|----|----|----|----|----|----|------------------|

| CODE DESCRIPTION                               | V <sub>REF</sub><br>6.40<br>(V) | V <sub>REF</sub><br>5.12<br>(V)                 | V <sub>REF</sub><br>4.80<br>(V) | V <sub>REF</sub><br>3.20<br>(V) | OF | B6 | B5 | В4 | В3 | B2 | B1 | DECIMAL<br>COUNT |

| Zero                                           | 0.00                            | 0.00                                            | 0.00                            | 0.00                            | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0                |

| 1 LSB                                          | 0.10                            | 0.08                                            | 0.075                           | 0.05                            | 0  | 0  | 0  | 0  | 0  | 0  | 1  | 1                |

| 2 LSB                                          | 0.20                            | 0.16                                            | 0.15                            | 0.10                            | 0  | 0  | 0  | 0  | 0  | 1  | 0  | 2                |

|                                                |                                 |                                                 | •                               |                                 |    |    |    | •  |    |    |    |                  |

|                                                |                                 |                                                 | •                               |                                 |    |    |    | •  |    |    |    |                  |

| •                                              |                                 |                                                 | •                               |                                 |    |    |    | •  |    |    |    | •                |

| •                                              |                                 |                                                 | •                               |                                 |    |    |    | •  |    |    |    | •                |

| <sup>1</sup> / <sub>2</sub> Full Scale - 1 LSB | 3.10                            | 2.48                                            | 2.325                           | 1.55                            | 0  | 0  | 1  | 1  | 1  | 1  | 1  | 31               |

| 1/ <sub>2</sub> Full Scale                     | 3.20                            | 2.56                                            | 2.40                            | 1.60                            | 0  | 1  | 0  | 0  | 0  | 0  | 0  | 32               |

| <sup>1</sup> / <sub>2</sub> Full Scale + 1 LSB | 3.30                            | 2.64                                            | 2.475                           | 1.65                            | 0  | 1  | 0  | 0  | 0  | 0  | 1  | 33               |

| •                                              |                                 |                                                 | •                               |                                 |    |    |    |    |    |    |    |                  |

| •                                              |                                 |                                                 | •                               |                                 |    |    |    | •  |    |    |    | •                |

| •                                              |                                 |                                                 | •                               |                                 |    |    |    | •  |    |    |    | •                |

|                                                |                                 |                                                 | •                               |                                 |    |    |    | •  |    |    |    | •                |

| Full Scale - 1 LSB                             | 6.20                            | 4.96                                            | 4.65                            | 3.10                            | 0  | 1  | 1  | 1  | 1  | 1  | 0  | 62               |

| Full Scale                                     | 6.30                            | 5.04                                            | 4.725                           | 3.15                            | 0  | 1  | 1  | 1  | 1  | 1  | 1  | 63               |

| Overflow                                       | 6.40                            | 5.12                                            | 4.80                            | 3.20                            | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 127              |

NOTE:

<sup>6.</sup> The voltages listed above are the ideal centers of each output code shown as a function of its associated reference voltage.

# **Device Operation**

A sequential parallel technique is used by the HI3306 converter to obtain its high speed operation. The sequence consists of the "Auto Balance" phase  $\phi 1$  and the "Sample Unknown" phase  $\phi 2$ . (Refer to the circuit diagram.) Each conversion takes one clock cycle (see Note). With the phase control low, the "Auto Balance" ( $\phi 1$ ) occurs during the High period of the clock cycle, and the "Sample Unknown" ( $\phi 2$ ) occurs during the low period of the clock cycle.

During the "Auto Balance" phase, a transmission-gate switch is used to connect each of 64 commutating capacitors to their associated ladder reference tap. Those tap voltages will be as follows:

$V_{TAP}(N) = [(V_{REF}/64) \times N] - [V_{REF}/(2 \times 64)],$ =  $V_{REF}[(2N - 1)/126],$

Where:  $V_{TAP}(N)$  = reference ladder tap voltage at point N,

$V_{REF}$  = voltage across  $V_{REF}$ - to  $V_{REF}$ +,

N = tap number (I through 64).

NOTE: This device requires only a single-phase clock. The terminology of  $\phi1$  and  $\phi2$  refers to the High and Low periods of the same clock.

The other side of the capacitor is connected to a single-stage inverting amplifier whose output is shorted to its input by a switch. This biases the amplifier at its intrinsic trip point, which is approximately,  $(V_{DD} - V_{SS})/2$ . The capacitors now charge to their associated tap voltages, priming the circuit for the next phase.

In the "Sample Unknown" phase, all ladder tap switches are opened, the comparator amplifiers are no longer shorted, and  $V_{\text{IN}}$  is switched to all 64 capacitors. Since the other end of the capacitor is now looking into an effectively open circuit, any voltage that differs from the previous tap voltage will appear as a voltage shift at the comparator amplifiers. All comparators whose tap voltages were lower than  $V_{\text{IN}}$  will drive the comparator outputs to a "low" state. All comparators whose tap voltages were higher than  $V_{\text{IN}}$  will drive the comparator outputs to a "high" state. A second, capacitor-coupled, auto-zeroed amplifier further amplifies the outputs.

The status of all these comparator amplifiers are stored at the end of this phase ( $\phi$ 2), by a secondary latching amplifier stage. Once latched, the status of the 64 comparators is decoded by a 64-bit 7-bit decode array and the results are clocked into a storage register at the rising edge of the next  $\phi$ 2.

A three-state buffer is used at the output of the 7 storage registers which are controlled by two chip-enable signals. CE1 will independently disable B1 through B6 when it is in a high state. CE2 will independently disable B1 through B6 and the overflow buffers when it is in the low state (Table 1).

To facilitate usage of this device a phase-control input is provided which can effectively complement the clock as it enters the chip. Also, an on-board Zener is provided for use as a reference voltage.

#### **Continuous Clock Operation**

One complete conversion cycle can be traced through the HI3306 via the following steps. (Refer to timing diagram, Figure 1.) With the phase control in a "High" state, the rising edge of the clock input will start a "sample" phase. During this entire "High" state of the clock, the 64 comparators will track the input voltage and the 64 latches will track the comparator outputs. At the falling edge of the clock, after the specified aperture delay, all 64 comparator outputs are captured by the 64 latches. This ends the "sample" phase and starts the "auto balance" phase for the comparators. During this "Low" state of the clock the output of the latches propagates through the decode array and a 7-bit code appears at the D inputs of the output registers. On the next rising edge of the clock, this 7-bit code is shifted into the output registers and appears with time delay to as valid data at the output of the three-state drivers. This also marks the start of a new "sample" phase, thereby repeating the conversion process for this next cycle.

#### Pulse Mode Operation

For sampling high speed nonrecurrent or transient data, the converter may be operated in a pulse mode in one of three ways. The fastest method is to keep the converter in the Sample Unknown phase,  $\phi 2$ , during the standby state. The device can now be pulsed through the Auto Balance phase with a single pulse. The analog value is captured on the leading edge of  $\phi 1$  and is transferred into the output registers on the trailing edge of  $\phi 1$ . We are now back in the standby state,  $\phi 2$ , and another conversion can be started, but not later than  $5\mu s$  due to the eventual droop of the commutating capacitors. Another advantage of this method is that it has the potential of having the lowest power drain. The larger the time ratio between  $\phi 2$  and  $\phi 1$ , the lower the power consumption. (See Timing Waveform, Figure 3.)

The second method uses the Auto Balance phase,  $\phi 1$ , as the standby state. In this state the converter can stay indefinitely waiting to start a conversion. A conversion is performed by strobing the clock input with two  $\phi 2$  pulses. The first pulse starts a Sample Unknown phase and captures the analog value in the comparator latches on the trailing edge. A second  $\phi 2$  pulse is needed to transfer the data into the output registers. This occurs on the leading edge of the second pulse. The conversion now takes slightly longer, but the repetition rate may be as slow as desired. The disadvantage to this method is the higher device dissipation due to the low ratio of  $\phi 2$  to  $\phi 1$ . (See Timing Waveform, Figure 3B.)

For applications requiring both indefinite standby and lowest power, standby can be in the  $\phi 2$  (Sample Unknown) state with two  $\phi 1$  pulses to generate valid data (see Figure 3C). Valid data now appears two full clock cycles after starting the conversion process.

#### Analog Input Considerations

The HI3306 input terminal is characterized by a small capacitance (see Specifications) and a small voltage-dependent current (See Typical Performance Curves). The

signal-source impedance should be kept low, however, when operating the HI3306 at high clock rates.

The HI3306 outputs a short (less than 10ns) current spike of up to several mA amplitude (See Typical Performance Curves) at the beginning of the sample phase. (To a lesser extent, a spike also appears at the beginning of auto balance.) The driving source must recover from the spike by the end of the same phase, or a loss of accuracy will result.

A locally terminated  $50\Omega$  or  $75\Omega$  source is generally sufficient to drive the HI3306. If gain is required, a high speed, fast settling operational amplifier, such as the HA-5033, HA-2542, or HA5020 is recommended.

#### **Digital Input And Output Interfacing**

The two chip-enable and the phase-control inputs are standard CMOS units. They should be driven from less than  $0.3 \times V_{DD}$  to at least  $0.7 \times V_{DD}$ . This can be done from 74HC series CMOS (QMOS), TTL with pull-up resistors, or, if  $V_{DD}$  is greater than the logic supply, open collector or open drain drivers plus pull-ups. (See Figure 20.)

The clock input is more critical to timing variations, such as  $\phi1$  becoming too short, for instance. Pull-up resistors should generally be avoided in favor of active drivers. The clock input may be capacitively coupled, as it has an internal  $50k\Omega$  feedback resistor on the first buffer stage, and will seek its own trip point. A clock source of at least  $1V_{P-P}$  is adequate, but extremely non-symmetrical waveforms should be avoided.

The output drivers have full rail-to-rail capability. If driving CMOS systems with  $V_{DD}$  below the  $V_{DD}$  of the HI3306, a CD74HC4050 or CD74HC4049 should be used to step down the voltage. If driving LSTTL systems, no step-down should be necessary, as most LSTTLs will take input swings up to 10V to 15V.

Although the output drivers are capable of handling typical data bus loading, the capacitor charging currents will produce local ground disturbances. For this reason, an external bus driver is recommended.

#### Increased Accuracy

In most cases the accuracy of the HI3306 should be sufficient without any adjustments. In applications where accuracy is of utmost importance, three adjustments can be made to obtain better accuracy; i.e., offset trim, gain trim, and midpoint trim.

#### Offset Trim

In general offset correction can be done in the preamp circuitry by introducing a DC shift to  $V_{IN}$  or by the offset trim of the operational amplifier. When this is not possible the  $V_{REF}$ - input can be adjusted to produce an offset trim. The theoretical input voltage to produce the first transition is  $^{1}/_{2}$  LSB. The equation is as follows:

$$V_{1N}$$

(0 to 1 transition) =  ${}^{1}/_{2}$  LSB =  ${}^{1}/_{2}$ ( $V_{REF}$ /64)

$$= V_{RFF}/128.$$

If  $V_{IN}$  for the first transition is less than the theoretical, then a single-turn 50 $\Omega$  pot connected between  $V_{REF}$ - and

ground will accomplish the adjustment. Set  $V_{IN}$  to  $^{1}/_{2}$  LSB and trim the pot until the 0 to 1 transition occurs.

If  $V_{IN}$  for the first transition is greater than the theoretical, then the  $50\Omega$  pot should be connected between  $V_{REF}$  and a negative voltage of about 2 LSBs. The trim procedure is as stated previously.

#### **Gain Trim**

In general the gain trim can also be done in the preamp circuitry by introducing a gain adjustment for the operational amplifier. When this is not possible, then a gain adjustment circuit should be made to adjust the reference voltage. To perform this trim,  $V_{\text{IN}}$  should be set to the 63 to overflow transition. That voltage is  $^{1}/_{2}$  LSB less than  $V_{\text{REF}}+$  and is calculated as follows:

$$V_{IN}$$

(63 to 64 transition) =  $V_{REF}$  -  $V_{REF}$ /128

=  $V_{REF}$ (127/128)

To perform the gain trim, first do the offset trim and then apply the required  $V_{\text{IN}}$  for the 63 to overflow transition. Now adjust  $V_{\text{RFF}}$ + until that transition occurs on the outputs.

#### **Midpoint Trim**

The reference center (RC) is available to the user as the midpoint of the resistor ladder. To trim the midpoint, the offset and gain trims should be done first. The theoretical transition from count 31 to 32 occurs at 31<sup>1</sup>/<sub>2</sub> LSBs. That voltage is as follows:

$$V_{IN}$$

(31 to 32 transition) = 31.5 ( $V_{REF}$ /64)

=  $V_{REF}$ (63/128)

An adjustable voltage follower can be connected to the RC pin or a  $2k\Omega$  pot can be connected between  $V_{REF}+$  and  $V_{REF}-$  with the wiper connected to RC. Set  $V_{IN}$  to the 31 to 32 transition voltage, then adjust the voltage follower or the pot until the transition occurs on the output bits.

The Reference Center point can also be used to create unique transfer functions. The user must remember, however, that there is approximately  $120\Omega$  in series with the RC pin.

# **Applications**

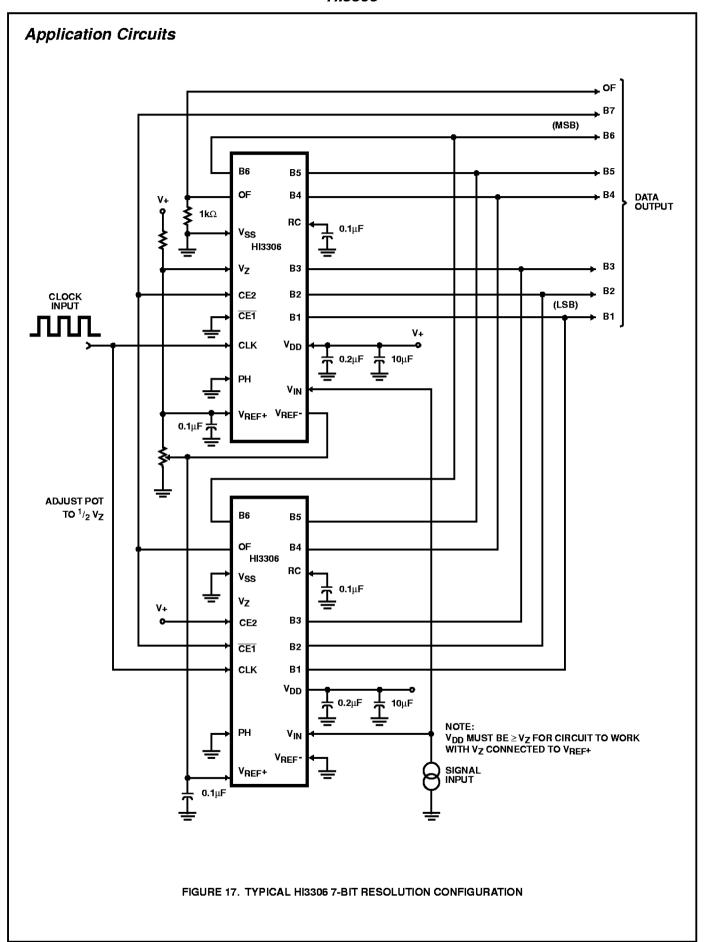

# 7-Bit Resolution

To obtain 7-bit resolution, two HI3306s can be wired together. Necessary ingredients include an open-ended ladder network, an overflow indicator, three-state outputs, and chipenabler controls - all of which are available on the HI3306.

The first step for connecting a 7-bit circuit is to totem-pole the ladder networks, as illustrated in Figure 17. Since the absolute resistance value of each ladder may vary, external trim of the mid-reference voltage may be required.

The overflow output of the lower device now becomes the seventh bit. When it goes high, all counts must come from the upper device. When it goes low, all counts must come from the lower device. This is done simply by connecting the lower overflow signal to the  $\overline{CE1}$  control of the lower A/D converter and the CE2 control of the upper A/D con-

verter. The three-state outputs of the two devices (bits 1 through 6) are now connected in parallel to complete the circuitry.

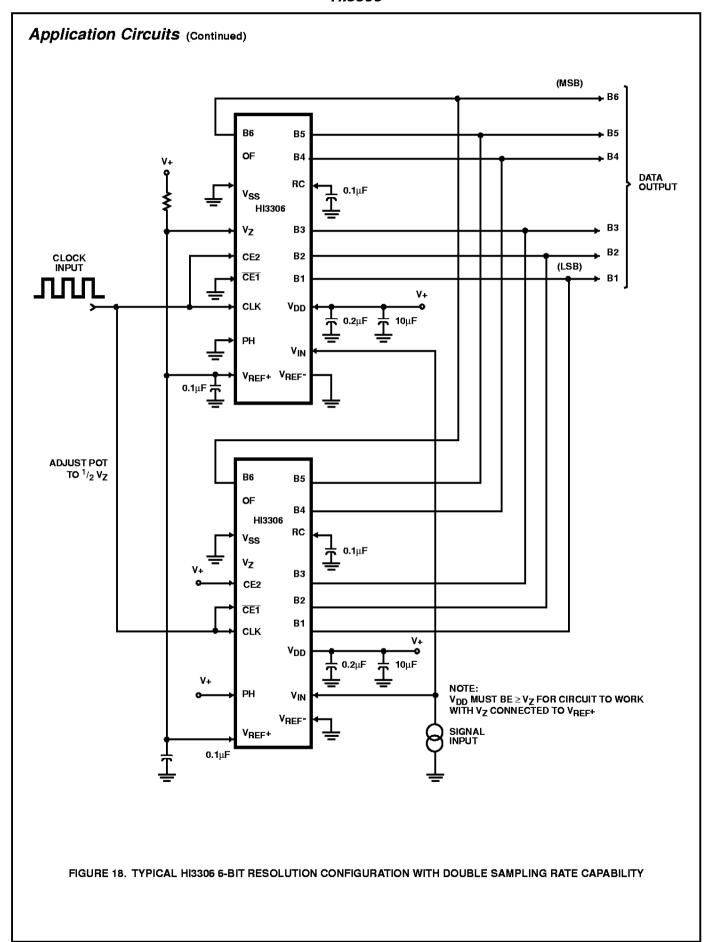

#### Doubled Sampling Speed

The phase control and both positive and negative true chip enables allow the parallel connection of two HI3306s to double the sampling speed. Figure 18 shows this configuration. One converter samples on the positive phase of the clock, and the second on the negative. The outputs are also alternately enabled. Care should be taken to provide a near square-wave clock it operating at close to the maximum clock speed for the devices.

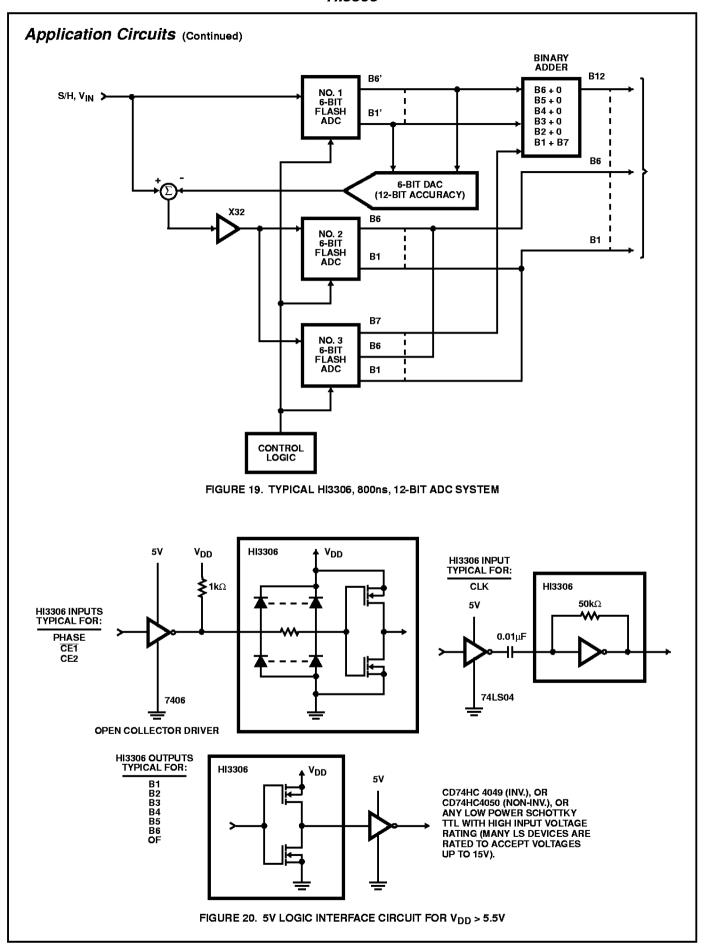

#### 8-Bit to 12-Bit Conversion Techniques

To obtain 8-bit to 12-bit resolution and accuracy, use a feed- forward conversion technique. Two A/D converters will be needed to convert up to 11 bits; three A/D converters to convert 12 bits. The high speed of the HI3306 allows 12-bit conversions in the 500ns to 900ns range.

The circuit diagram of a high-speed 12-bit A/D converter is shown in Figure 19. In the feed-forward conversion method two sequential conversions are made. Converter A first does a coarse conversion to 6 bits. The output is applied to a 6-bit D/A converter whose accuracy level is good to 12 bits. The D/A converter output is then subtracted from the input voltage, multiplied by 32, and then converted by a second flash A/D converter, which is connected in a 7-bit configuration. The answers from the first and second conversions are added together with bit 1 of the first conversion overlapping bit 7 of the second conversion.

When using this method, take care that:

- The linearity of the first converter is better than <sup>1</sup>/<sub>2</sub> LSB.

- An offset bias of 1 LSB (1/64) Is subtracted from the first conversion since the second converter is unipolar.

- The D/A converter and its reference are accurate to the total number of bits desired for the final conversion (the A/D converter need only be accurate to 6 bits).

The first converter can be offset-biased by adding a  $20\Omega$  resistor at the bottom of the ladder and increasing the reference voltage by 1 LSB. If a 6.4V reference is used in the system, for example, then the first HI3306 will require a 6.5V reference.

#### **Definitions**

#### **Dynamic Performance Definitions**

Fast Fourier Transform (FFT) techniques are used to evaluate the dynamic performance of the converter. A low distortion sine wave is applied to the input, it is sampled, and the output is stored in RAM. The data is then transformed into the frequency domain with a 4096 point FFT and analyzed to evaluate the dynamic performance of the A/D. The sine wave input to the part is -0.5dB down from full scale for all these tests.

#### Signal-to-Noise (SNR)

SNR is the measured RMS signal to RMS noise at a specified input and sampling frequency. The noise is the RMS sum of all of the spectral components except the fundamental and the first five harmonics.

#### Signal-to-Noise + Distortion Ratio (SINAD)

SINAD is the measured RMS signal to RMS sum of all other spectral components below the Nyquist frequency excluding DC.

#### Effective Number of Bits (ENOB)

The effective number of bits (ENOB) is derived from the SINAD data. ENOB is calculated from:

ENOB =  $(SINAD - 1.76 + V_{COBB})/6.02$ ,

where:  $V_{CORR} = 0.5dB$ .

#### Total Harmonic Distortion (THD)

THD is the ratio of the RMS sum of the first 5 harmonic components to the RMS value of the measured input signal.

# Operating and Handling Considerations

#### HANDLING

All inputs and outputs of Harris CMOS devices have a network for electrostatic protection during handling. Recommended handling practices for CMOS devices are described in AN6525. "Guide to Better Handling and Operation of CMOS Integrated Circuits."

#### **OPERATING**

#### Operating Voltage

During operation near the maximum supply voltage limit, care should be taken to avoid or suppress power supply turn-on and turn-off transients, power supply ripple, or ground noise; any of these conditions must not cause  $V_{DD}$  -  $V_{SS}$  to exceed the absolute maximum rating.

#### Input Signals

To prevent damage to the input protection circuit, input signals should never be greater than  $V_{DD}$  nor less than  $V_{SS}$ . Input currents must not exceed 20mA even when the power supply is off. The Zener (pin 4) is the only terminal allowed to exceed  $V_{DD}$ .

#### **Unused Inputs**

A connection must be provided at every input terminal. All unused input terminals must be connected to either  $V_{DD}$  or  $V_{SS}$ , whichever is appropriate.

# **Output Short Circuits**

Shorting of outputs to  $V_{DD}$  or  $V_{SS}$  may damage CMOS devices by exceeding the maximum device dissipation.